# PRODUCT OVERVIEW

# **CALMRISC OVERVIEW**

The S3CB018/FB018 single-chip CMOS microcontroller is designed for high performance using Samsung's newest 8-bit CPU core, CalmRISC.

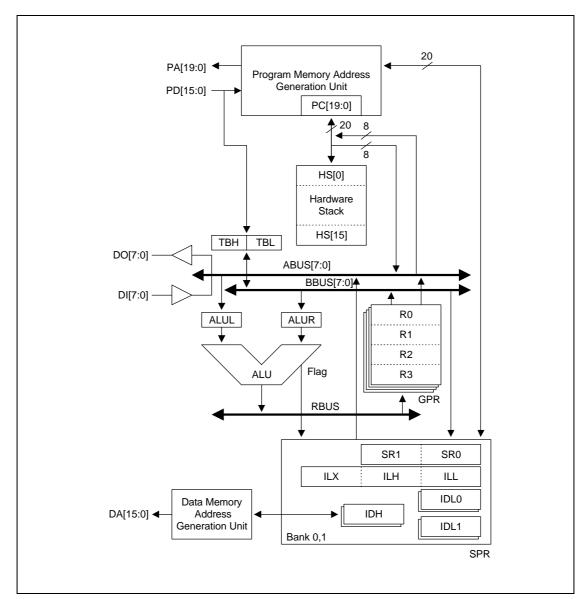

CalmRISC is an 8-bit low power RISC microcontroller. Its basic architecture follows Harvard style, that is, it has separate program memory and data memory. Both instruction and data can be fetched simultaneously without causing a stall, using separate paths for memory access. Represented below is the top block diagram of the CalmRISC microcontroller.

## S3CB018/FB018 OVERVIEW

## FEATURES SUMMARY

### CPU

8-Bit RISC architecture

#### Memory

- ROM: 4 Kword (8 K-byte)

- RAM: 3072 (1024+2048) byte 1024 (X-memory) byte 2048 (Y-memory) byte

### Stack

• size: maximum 16 (word)-level

#### 26 I/O Pins

• I/O: 26 pins, including 8 S/W open drain pins

#### 8-Bit Basic Timer

- Programmable interval timer

- 8 kinds of clock source

#### Watchdog Timer

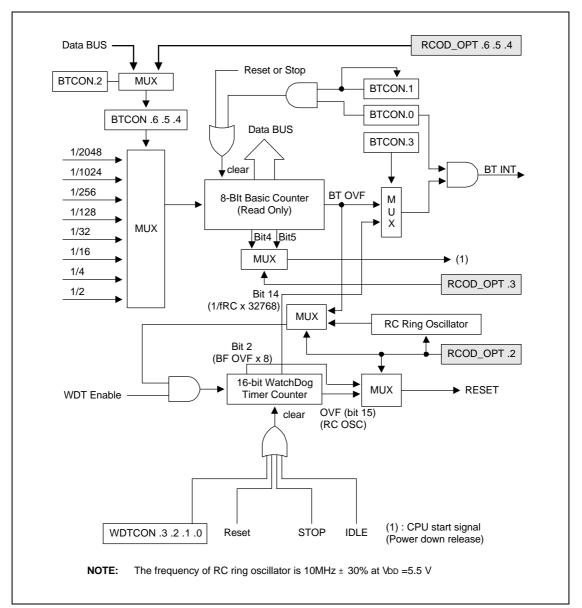

• System reset when 11-bit counter overflows

#### 16-Bit Timer/Counter

- Programmable interval timer

- Two 8-bit timer counter mode and one 16-bit timer counter mode, selectable by S/W

#### Watch Timer

- Real time clock or interval time measurement

- Four frequency outputs for buzzer sound

#### 8-Bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive mode

- LSB first or MSB first transmission selectable

- Internal and external clock source

#### 16-Bit Serial I/O Interface

- 16-bit transmit/receive mode

- External clock source

## Coprocessor

- MAC 816

- 8 x 16, 16 x 16 Multiply and Accumulation

- Arithmetic operation

### **Two Power-Down Modes**

- Idle mode: only CPU clock stop

- Stop mode: selected system clock and CPU clock stop

#### **Oscillation Sources**

- Crystal and Ceramic (0.4-20MHz), RC Oscillation

- Programmable oscillation source

#### Instruction Execution Times

- 50ns at 20MHz for 1 cycle instruction

- 100ns at 20MHz for 2 cycle instruction

Figure 1-1. Top Block Diagram of CalmRISC

The CalmRISC building blocks consist of:

- An 8-bit ALU

- 16 general purpose registers (GPR)

- 11 special purpose registers (SPR)

- 16-level hardware stack

- Program memory address generation unit

- Data memory address generation unit

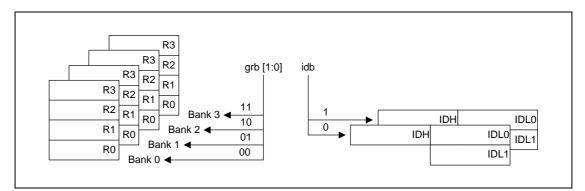

16 GPR's are grouped into four banks (Bank0 to Bank3) and each bank has four 8-bit registers (R0, R1, R2, and R3). SPR's, designed for special purposes, include status registers, link registers for branch-link instructions, and data memory index registers. The data memory address generation unit provides the data memory address (denoted as *DA[15:0]* in the top block diagram) for a data memory access instruction. Data memory contents are accessed through *DI[7:0]* for read operations and *DO[7:0]* for write operations. The program memory address generation unit contains a program counter, PC[19:0], and supplies the program memory address through *PA[19:0]* and fetches the corresponding instruction through *PD[15:0]* as the result of the program memory access. CalmRISC has a 16-level hardware stack for low power stack operations as well as a temporary storage area.

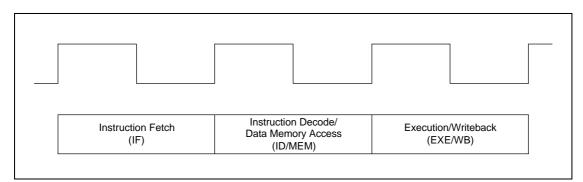

CalmRISC has a 3-stage pipeline as described below:

Figure 1-2. CalmRISC Pipeline Diagram

As can be seen in the pipeline scheme, CalmRISC adopts a register-memory instruction set. In other words, data memory where R is a GPR, can be one operand of an ALU instruction as shown below:

The first stage (or cycle) is Instruction Fetch stage (IF for short), where the instruction pointed to by the program counter, PC[19:0], is read into the Instruction Register (IR for short). The second stage is Instruction Decode and Data Memory Access stage (ID/MEM for short), where the fetched instruction (stored in IR) is decoded and data memory access is performed, if necessary. The final stage is Execute and Write-back stage (EXE/WB), where the required ALU operation is executed and the result is written back into the destination registers.

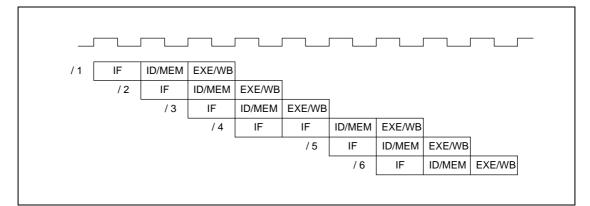

Since CalmRISC instructions are pipelined, the next instruction fetch is not postponed until the current instruction is completely finished, but is performed immediately after the current instruction fetch is done. The pipeline stream of instructions is illustrated in the following diagram.

1-4

Figure 1-3. CalmRISC Pipeline Stream Diagram

Most CalmRISC instructions are 1-word instructions, while same branch instructions such as "LCALL" and "LJT" instructions are 2-word instructions. In Figure 1-3, the instruction,  $I_4$ , is a long branch instruction and it takes two clock cycles to fetch the instruction. As indicated in the pipeline stream, the number of clocks per instruction (CPI) is 1 except for long branches, which take 2 clock cycles per instruction.

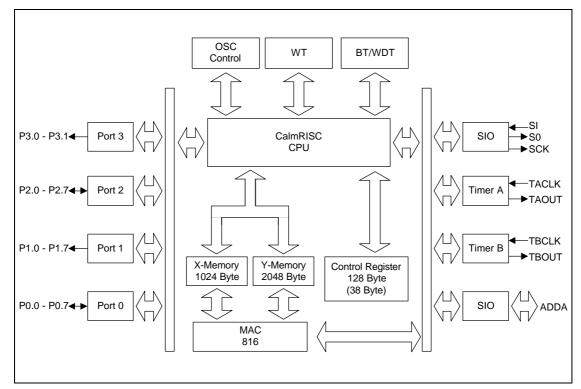

Figure 1-4. S3CB018/FB018 Block Diagram

## **PIN ASSIGNMENTS**

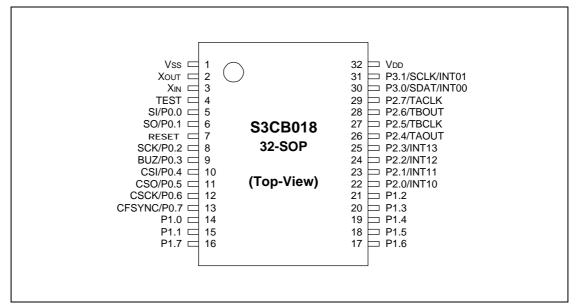

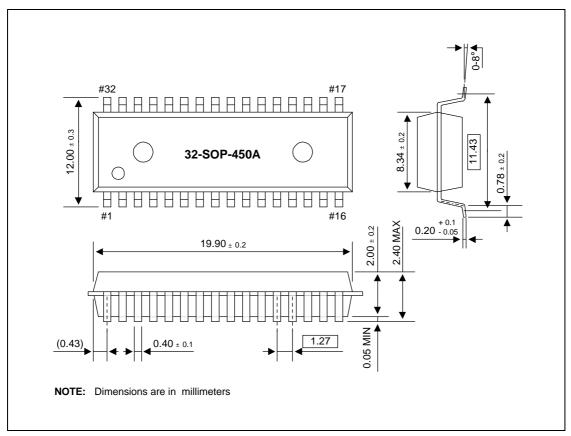

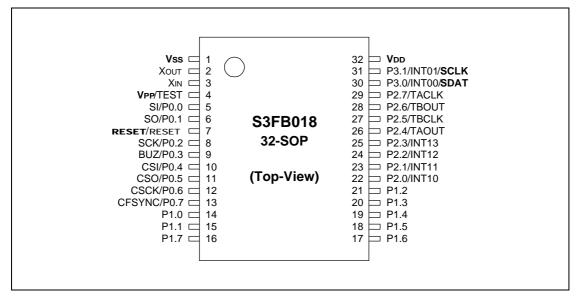

Figure 1-5. 32-SOP Pin Assignment

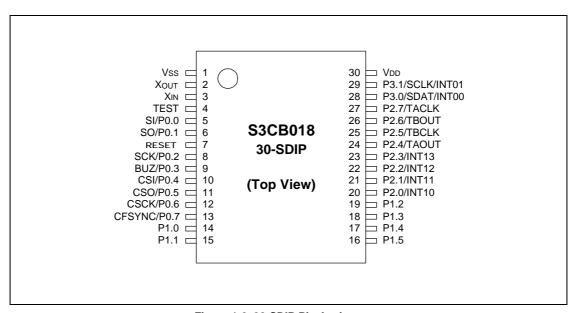

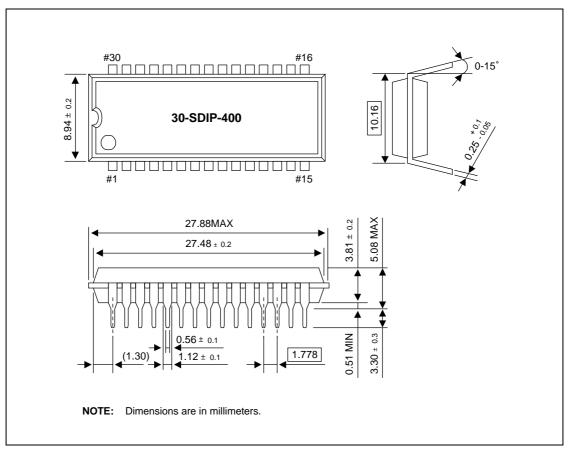

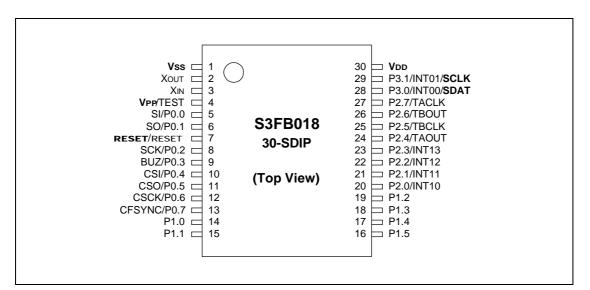

Figure 1-6. 30-SDIP Pin Assignment

# **I/O PIN DESCRIPTION**

| Pin<br>Name | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                         | Circuit<br>Type | Share<br>Pins                                    |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------|

| P0.0-P0.7   | I/O         | I/O port with bit programmable pins; Input and output mode are selectable by software; Software assignable pull-up. P0.4-P0.7 can be used as inputs for comparator input CIN0-CIN3.; Alternately they can be used as SI, SO, SCK, BUZ, CSI, CSO, CSCK, CFSYNC.                          | D-2<br>F-10     | SI, SO, SCK<br>BUZ, CSI,<br>CSO, CSCK,<br>CFSYNC |

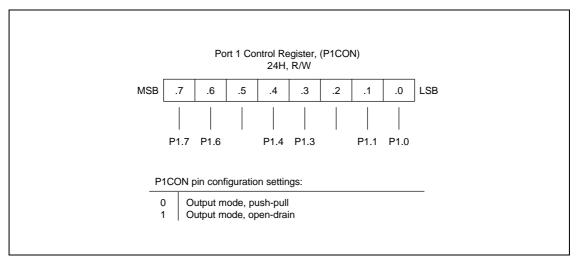

| P1.0-P1.7   | 0           | Output port with bit programmable pins; Push-pull output mode<br>and open-drain output mode are selected by software;<br>Software assignable pull-up.                                                                                                                                   | E-2             |                                                  |

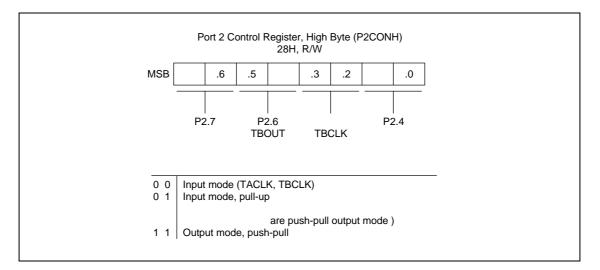

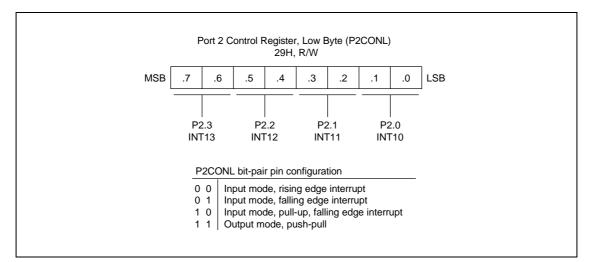

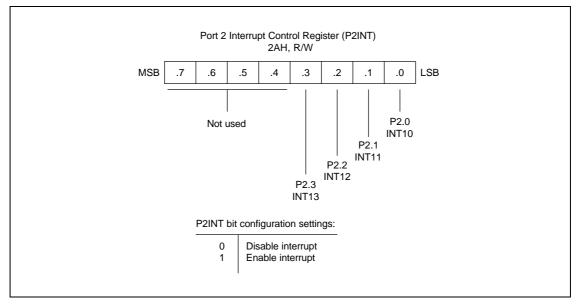

| P2.0-P2.7   | I/O         | I/O port with bit programmable pins; Input and output mode are<br>selectable by software; Software assignable pull-up; P2.0-P2.3<br>can be used as inputs for external interrupts INT10-INT13.<br>(with noise filter); Alternately they can be used as TAOUT,<br>TACLK or TBOUT, TBCLK. |                 | INT10-INT13<br>TAOUT<br>TACLK<br>TBOUT<br>TBCLK  |

| P3.0-P3.1   | I/O         | I/O port with bit programmable pins; Input or output mode<br>selected by software; software assignable pull-up; P3.0-P3.1<br>can be used as inputs for external interrupts INT00-INT01.<br>(with noise filter and interrupt polarity control)                                           | D-4             | INT00-INT01                                      |

| Pin<br>Name | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                         | Circuit<br>Type | Share<br>Pins                                    |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------|

| P0.0-P0.7   | I/O         | I/O port with bit programmable pins; Input and output mode are selectable by software; Software assignable pull-up. P0.4-P0.7 can be used as SI, SO, SCK, BUZ, CSI, CSO, CSCK, CFSYNC, Alternately.                                                                                     | D-2<br>F-10     | SI, SO, SCK<br>BUZ, CSI,<br>CSO, CSCK,<br>CFSYNC |

| P1.0-P1.5   | 0           | O port with bit programmable pins; Push-pull output mode and open-drain output mode are selected by software; Software assignable pull-up.                                                                                                                                              | E-2             |                                                  |

| P2.0-P2.7   | I/O         | I/O port with bit programmable pins; Input and output mode are<br>selectable by software; Software assignable pull-up; P2.0-P2.3<br>can be used as inputs for external interrupts INT10-INT13.<br>(with noise filter); Alternately they can be used as TAOUT,<br>TACLK or TBOUT, TBCLK. | D-4<br>D-2      | INT10-INT13<br>TAOUT<br>TACLK<br>TBOUT<br>TBCLK  |

| P3.0-P3.1   | I/O         | I/O port with bit programmable pins; Input or output mode<br>selected by software; software assignable pull-up; P3.0-P3.1<br>can be used as inputs for external interrupts INT00-INT01.<br>(with noise filter and interrupt polarity control)                                           | D-4             | INT00-INT01                                      |

NOTE: In S3CB018/FB018, the CSI, CSO, CSCK, CFSYNC pins are shared with P0.7-P0.4.

| Pin Name                           | Pin Type | Description                                                                                                                                           |  |

|------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CSI                                | I        | AD/DA Serial Input (from codec)                                                                                                                       |  |

| CSO                                | 0        | AD/DA Serial Output (to codec)                                                                                                                        |  |

| CSCK                               | I        | AD/DA Serial Clock (from codec)                                                                                                                       |  |

| CFSYNC                             | I        | AD/DA Sync signal (from codec)                                                                                                                        |  |

| SI                                 | I/O      | Serial data input                                                                                                                                     |  |

| SO                                 | I/O      | Serial data output                                                                                                                                    |  |

| SCK                                | I/O      | Serial I/O interface clock signal                                                                                                                     |  |

| BUZ                                | I/O      | 0.5 kHz, 1 kHz, 2 kHz, or 4 kHz frequency output at 4.19 MHz for buzzer sound                                                                         |  |

| INT10-INT13                        | I        | External interrupts. Stop release. Can't be masked by S/W individually but wholly.                                                                    |  |

| TAOUT                              | I/O      | Timer A interval mode output                                                                                                                          |  |

| TACLK                              | I/O      | Timer A counter external clock input                                                                                                                  |  |

| TBOUT                              | I/O      | Timer B interval mode output                                                                                                                          |  |

| TBCLK                              | I/O      | Timer B counter external clock input                                                                                                                  |  |

| INT00-INT01                        | I        | External interrupts. Stop release. Can be masked by S/W individually.                                                                                 |  |

| SDAT                               | I        | Serial data for Programmable memory                                                                                                                   |  |

| SCLK                               | I        | Serial clock for Programmable memory                                                                                                                  |  |

| VDD                                | -        | Power supply                                                                                                                                          |  |

| VSS                                | -        | Ground                                                                                                                                                |  |

| TEST                               | -        | Test signal input                                                                                                                                     |  |

| RESET                              |          | Reset signal                                                                                                                                          |  |

| X <sub>IN</sub> , X <sub>OUT</sub> | _        | Crystal, ceramic and RC oscillator signal for system clock (For external clock input, use $X_{IN}$ and input $X_{IN}$ 's reverse phase to $X_{OUT}$ ) |  |

# Table 1-3. I/O Pin Description

## **PIN ASSIGNMENTS**

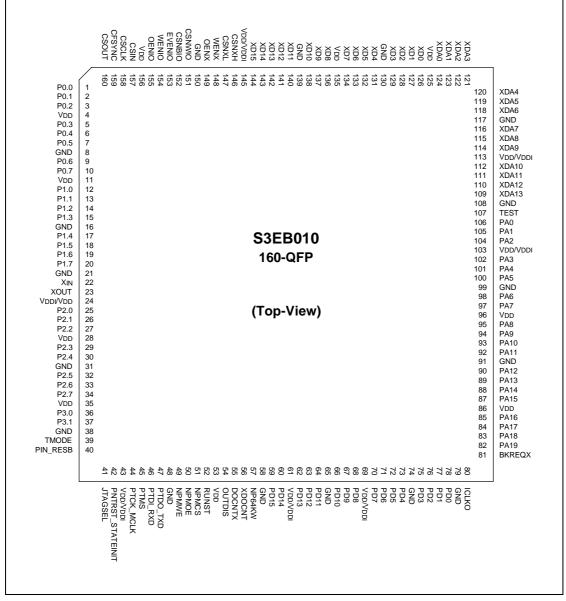

### Figure 1-7. S3EB010 Pin Diagram

| No.    | Pin Name             | Pin Type | Description                                         |

|--------|----------------------|----------|-----------------------------------------------------|

| 1-3    | P0.0-P0.2            | I/O      | Port 0                                              |

| 5-9    | P0.3-P0.7            |          |                                                     |

| 12-15  | P1.0-P1.3            | 0        | Port 1                                              |

| 17-20  | P1.4-P1.7            |          |                                                     |

| 22     | X <sub>IN</sub>      | I        | Clock In                                            |

| 23     | X <sub>OUT</sub>     | 0        | Clock Out                                           |

| 25-27  | P2.0-P2.2            | I/O      | Port 2                                              |

| 29, 30 | P2.3, P2.4           |          |                                                     |

| 32, 34 | P2.5-P2.7            |          |                                                     |

| 36, 37 | P3.0, P3.1           | I/O      | Port 3                                              |

| 39     | TMODE                | I        | Test Mode pin; 1: skip warm-up time, 0: normal mode |

| 40     | PIN_RESB             | I        | Asynchronous reset, active low                      |

| 41     | JTAGSEL              | I        | JTAG mode select; 1: parallel, 0: serial            |

| 42     | PNTRST_STSTEINI<br>T | I        | JTAG/UART pin                                       |

| 44     | PTCK_MCLK            | I        | JTAG/UART pin                                       |

| 45     | PTMS                 | I        | JTAG/UART pin                                       |

| 46     | PTDI_RXD             | I        | JTAG/UART pin                                       |

| 47     | PTDO_TXD             | 0        | JTAG/UART pin                                       |

| 49     | NPMWE                | 0        | Program Memory Write Enable, active low             |

| 50     | NPMOE                | 0        | Program Memory Output Enable, active low            |

| 51     | NPMCS                | 0        | Program Memory Chip Select, active low              |

| 52     | RUNST                | 0        | Run Status Indicator                                |

| 54     | OUTDIS               | I        | I/O PAD Disable for debugger                        |

| 55     | DOCNTX               | I        | Data Bus Output Control                             |

| 56     | XDOCNTX              | I        | External X-Memory Data Bus Output Control           |

| 57     | NPM64KW              | I        | Up to 64KW Program Memory, active low               |

| 59, 60 | PD15-PD14            | I/O      | Program Memory Data Bus                             |

| 62-64  | PD13-PD11            |          |                                                     |

| 66-68  | PD10-PD8             |          |                                                     |

| 70-73  | PD7-PD4              |          |                                                     |

| 75-78  | PD3-PD0              |          |                                                     |

Table 1-4. Evaluation Chip Pin Descriptions

1-11

| No.     | Pin Name     | Pin Type | Description                                             |

|---------|--------------|----------|---------------------------------------------------------|

| 80      | ICLKO        | 0        | ICLK Output                                             |

| 81      | BKREQX       | I        | Break input for debugger                                |

| 82-85   | PA19-PA16    | 0        | Program Memory Address                                  |

| 87-90   | PA15-PA12    |          |                                                         |

| 92-95   | PA11-PA8     |          |                                                         |

| 97, 98  | PA7, PA6     |          |                                                         |

| 100-102 | PA5-PA3      |          |                                                         |

| 104-106 | PA2-PA0      |          |                                                         |

| 107     | TEST         | I        | Test pin for debugger                                   |

| 109-112 | XDA13-XDA10  | 0        | External X-Memory Address                               |

| 114-116 | XDA9-XDA7    |          |                                                         |

| 118-124 | XDA6-XDA0    |          |                                                         |

| 126-129 | XD0-XD3      | I/O      | External X-Memory Data Bus                              |

| 131-134 | XD4-XD7      |          |                                                         |

| 136-138 | XD8-XD10     |          |                                                         |

| 140-144 | XD11-XD15    |          |                                                         |

| 146     | CSNXH        | 0        | External X-Memory High Byte Chip Select, active low     |

| 147     | CSNXL        | 0        | External X-Memory Low Byte Chip Select, active low      |

| 148     | WENX         | 0        | External X-Memory Write Enable, active low              |

| 149     | OENX         | 0        | External X-Memory Output Enable, active low             |

| 151     | CSNWIO       | 0        | External I/O Word Chip Select, active low               |

| 152     | CSNBIO       | 0        | External I/O Byte Chip Select, active low               |

| 153     | EVENIO       | 0        | External I/O Even Indicator; 1:Even, 0: Odd             |

| 154     | WENIO        | 0        | External I/O Write Enable, active low                   |

| 155     | OENIO        | 0        | External I/O Output Enable, active low                  |

| 157     | CSIN         | I        | AD / DA Serial Input (from codec)                       |

| 158     | CSCLK        | I        | AD / DA Serial Clock (from codec)                       |

| 159     | CFSYNC       | I        | AD / DA Sync signal (from codec)                        |

| 160     | CSOUT        | 0        | AD / DA Serial Output (to codec)                        |

| VDD     | Power supply | _        | 4, 11, 24, 28, 35, 43, 53, 61, 69, 86, 96, 103, 113     |

|         |              |          | 125, 135, 145, 156                                      |

| GND     | Ground       | _        | 8, 16, 21, 31, 38, 48, 58, 65, 74, 79, 91, 99, 108, 117 |

|         |              |          | 130, 139, 150                                           |

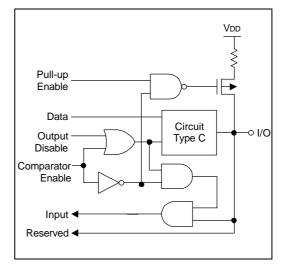

## **PIN CIRCUIT DIAGRAMS**

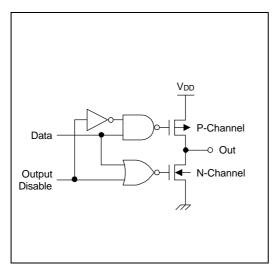

Figure 1-8. Pin Circuit Type B (RESET)

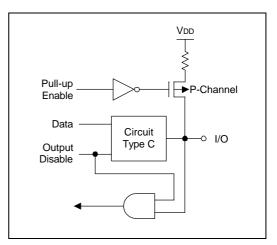

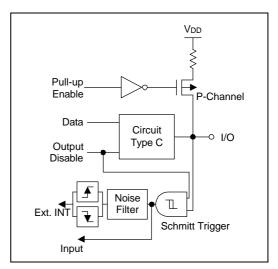

Figure 1-9. Pin Circuit Type C

Figure 1-10. Pin Circuit Type D-2 (P0.0-P0.3, P2.4-P2.7)

Figure 1-11. Pin Circuit Type D-4 (P2.0-P2.3, P3)

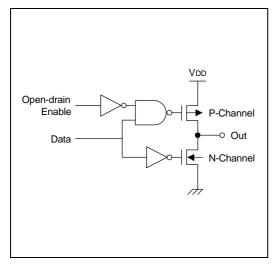

Figure 1-12. Pin Circuit Type E-2 (P1)

Figure 1-13. Pin Circuit Type F-10 (P0.4-P0.7)

# **2** ADDRESS SPACE

# OVERVIEW

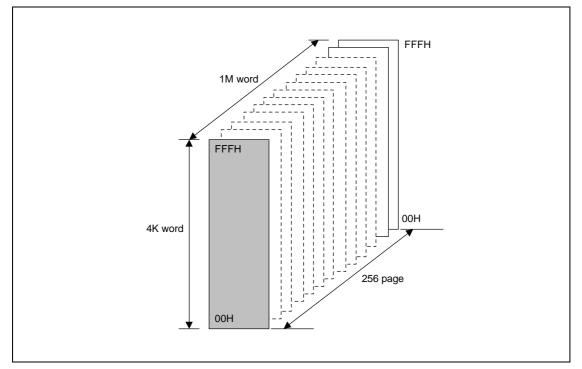

CalmRISC has 20-bit program address lines, *PA[19:0]*, which support up to 1M words of program memory. The 1 M word program memory space is divided into 256 pages, and each page is 4K word long, as shown in the next page. The upper 8 bits of the program counter, PC[19:12], point to a specific page and the lower 12 bits, PC[11:0], specify the offset address of the page.

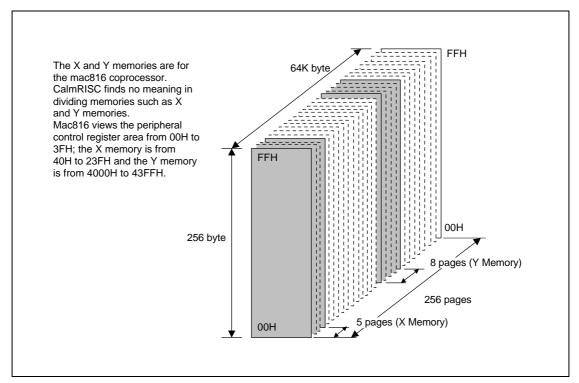

CalmRISC also has 16-bit data memory address lines, DA[15:0], which support up to 64K bytes of data memory. The 64K byte data memory space is divided into 256 pages, and each page has 256 bytes. The upper 8 bits of the data address, DA[15:8], point to a specific page, and the lower 8 bits, DA[7:0], specify the offset address of the page.

## **PROGRAM MEMORY (ROM)**

Figure 2-1. Program Memory Organization

For example, if PC[19:0] = 5F79AH, the page index pointed to by PC is 5FH and the offset in the page is 79AH. If the current PC[19:0] = 5EFFFH and the instruction pointed to by the current PC, i.e., the instruction at the address 5EFFFH is *not* a branch instruction, the next PC becomes 5E000H, *not* 5F000H. In other words, the instruction sequence wraps around at the page boundary, unless the instruction at the boundary (in the above example, at 5EFFFH) is a long branch instruction. The only way to change the program page is by long branches (LCALL, LLNK, and LJP), where the absolute branch target address is specified. For example, if the current PC[19:0] = 047ACH (the page index is 04H and the offset is 7ACH) and the instruction pointed to by the current PC, i.e., the instruction at the address 047ACH, is "LJP A507FH" (jump to the program address A507FH), then the next PC[19:0] = A507FH, which means that the page and the offset are changed to A5H and 07FH, respectively. On the other hand, the short branch instructions cannot change the page indices.

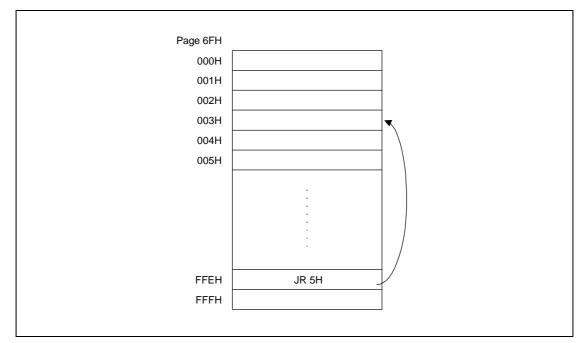

Suppose the current PC is 6FFFEH and its instruction is "JR 5H" (jump to the program address PC + 5H). Then the next instruction address is 6F003H, not 70003H. In other words, the branch target address calculation also wraps around with respect to a page boundary. This situation is illustrated below:

Figure 2-2. Relative Jump Around Page Boundary

Programmers do not have to manually calculate the offset and insert extra instructions for a jump instruction across page boundaries. The compiler and the assembler for CalmRISC are in charge of producing appropriate codes for it.

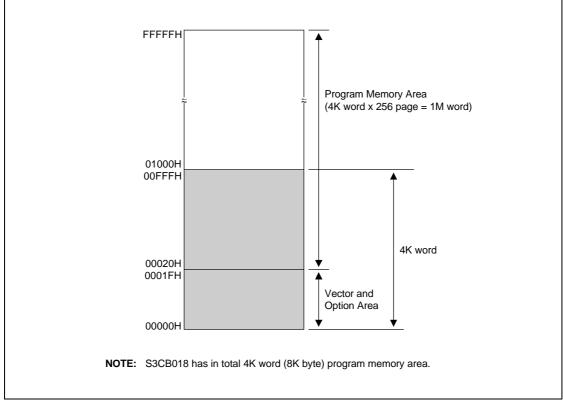

Figure 2-3. Program Memory Layout

Addresses from 00000H to 00004H are used as the vector addresses for the exceptions, and 0001EH and 0001FH are used for the option only. Aside from these addresses others are reserved in the vector and option areas. Program memory area from addresses 00020H to FFFFFH can be used for normal programs.

S3CB018/FB018's program memory is 4K word (8K byte) long, so addresses from 00020H to 00FFFH are the program memory area.

## ROM CODE OPTION (RCOD\_OPT)

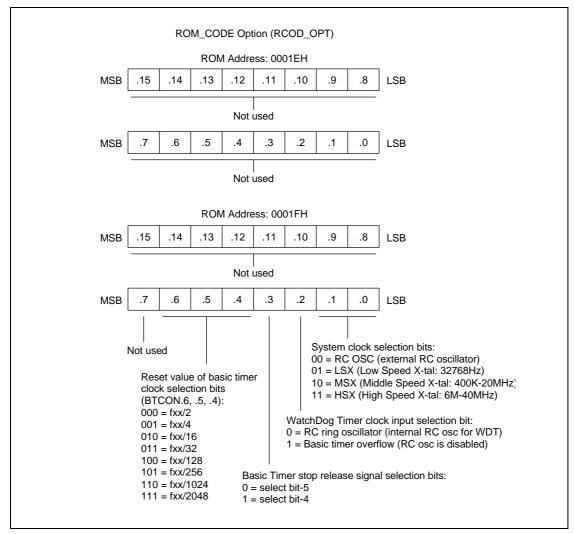

Just after power on, the oscillator becomes one of the four types of oscillators, RC, LSX, MSX and HSX, by the value of RCOD\_OPT, which is located at 0001EH and 0001FH in program memory. The address 0001EH and the high byte of address 0001FH are not used in S3CB018/FB018.

For example, if you program as below:

| rcod_opt | 001EH, 0FFFFH |

|----------|---------------|

| rcod_opt | 001FH, 0FF80H |

- If the watchdog timer overflows, the hardware reset exception would be serviced.

- The basic timer counter clock input is fxx/2048 after reset (by bit.6, .5, .4).

- BTCNT.5 is the CPU stop release signal (by bit.3).

- Basic timer overflow is the watchdog timer clock input (by bit.2).

- HSX (high speed oscillator) is the main system oscillator (by bit.1, .0).

If you do not program any values in these option, then the default value is "1". Therefore, in these cases the address 0001EH becomes the value of "FFH".

In S3EB010, the RCOD\_OPT is not available. Here the basic timer counter's clock input is fxx/2048; the stop release signal is the bit.5 of basic timer counter. The main system oscillator is the crystal oscillator(0.4–20MHz). The watchdog timer overflow produces the reset operation. In this state, it is fixed and not programmable in S3EB010.

The RCOD\_OPT is programmable only in S3CB018/FB018.

Figure 2-4. ROM Code Option (RCOD\_OPT)

## DATA MEMORY ORGANIZATION

The total data memory address space is 64K byte, addressed by *DA[15:0]*, which is also divided into 256 pages, Each page consists of 256 bytes as shown below.

Figure 2-5. Data Memory Map

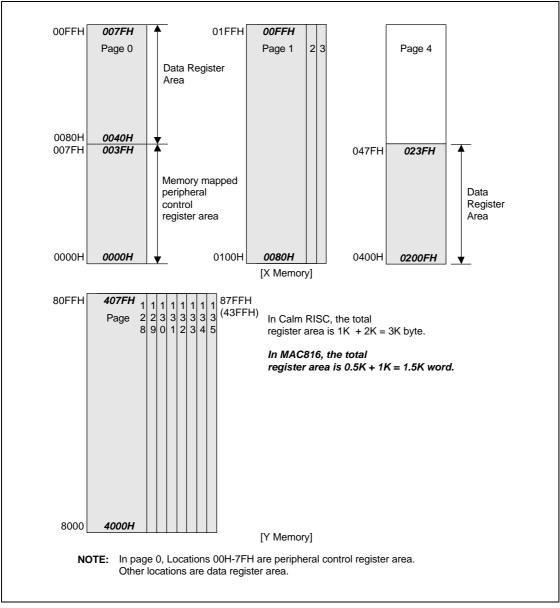

The data memory page is indexed by an SPR, IDH. In data memory index addressing mode, 16-bit data memory address is composed of two 8-bit SPR's, IDH[7:0] and IDL0[7:0] (or IDH[7:0] and IDL1[7:0]). IDH[7:0] points to a page index and IDL0[7:0] (or IDL1[7:0]) represents the page offset. In data memory direct addressing mode, an 8-bit direct address, adr[7:0], specifies the page offset pointed to by IDH[7:0] (See the details for direct addressing mode in the instruction sections). Unlike the program memory organization, data memory address does *not* wrap around. In other words, data memory index addressing with modification performs an addition or a subtraction operation on the whole 16-bit addresses of IDH[7:0] and IDL0[7:0] (or IDL1[7:0]) and updates IDH[7:0] and IDL0[7:0] (or IDL1[7:0]) accordingly. Suppose IDH[7:0] is 0FH and IDL0[7:0] is FCH and the modification on the index registers, IDH[7:0] and IDL0[7:0], is increment by 5H. Then after the modification (i.e., 0FFCH + 5 = 1001H), IDH[7:0] and IDL0[7:0] become 10H and 01H, respectively.

The S3CB018/FB018 has a total of 3072 bytes of data register address from 0000H to 047FH and from 8000H to 87FFH. Here the area from 0000H to 007FH is for peripheral control, Aside from this area the other area is for data memory. *Mac*816 views the peripheral control register area from 0000H to 003FH; X memory is from 0040H to 23FH, and Y memory is from 4000H to 43FFH.

# **3** REGISTERS

# OVERVIEW

The registers of CalmRISC are grouped into 2 parts: general purpose registers and special purpose registers.

| Registers                       |                | Mnemonics | Description                                            | Reset Value |

|---------------------------------|----------------|-----------|--------------------------------------------------------|-------------|

| General Purpose Registers (GPR) |                | R0        | General Register 0                                     | Unknown     |

|                                 |                | R1        | General Register 1                                     | Unknown     |

|                                 |                | R2        | General Register 2                                     | Unknown     |

|                                 |                |           | General Register 3                                     | Unknown     |

| Special Purpose                 | Group 0 (SPR0) | IDL0      | Lower Byte of Index Register 0                         | Unknown     |

| Registers (SPR)                 |                | IDL1      | Lower Byte of Index Register 1                         | Unknown     |

|                                 |                | IDH       | Higher Byte of Index Register                          | Unknown     |

|                                 |                | SR0       | Status Register 0                                      | 00H         |

|                                 | Group 1 (SPR1) | ILX       | Instruction Pointer Link Register for<br>Extended Byte | Unknown     |

|                                 |                | ILH       | Instruction Pointer Link Register for<br>Higher Byte   | Unknown     |

|                                 |                | ILL       | Instruction Pointer Link Register for Lower Byte       | Unknown     |

|                                 |                | SR1       | Status Register 1                                      | Unknown     |

GPR's can be used in most instructions such as ALU instructions, stack instructions, load instructions, *etc* (See the instruction set sections). From the programming standpoint, they have almost no restriction whatsoever. CalmRISC has 4 banks of GPR's and each bank has 4 registers, R0, R1, R2, and R3. Hence, 16 GPR's in total are available. The GPR bank switching can be done by setting an appropriate value in SR0[4:3] (See SR0 for details). The ALU operations among GPR's from different banks are *not* allowed.

SPR's are designed for their own dedicated purposes. They have some restrictions in terms of instructions that can access them. For example, direct ALU operations cannot be performed on SPR's. However, data transfers between a GPR and an SPR are allowed and stack operations with SPR's are also possible (See the instruction sections for details).

3-1

#### INDEX REGISTERS: IDH, IDL0 AND IDL1

IDH in concatenation with IDL0 (or IDL1) forms a 16-bit data memory address. Note that CalmRISC's data memory address space is 64 K byte (addressable by 16-bit addresses). Basically, IDH points to a page index and IDL0 (or IDL1) corresponds to an offset of the page. Like GPR's, the index registers are 2-way banked. There are 2 banks in total, each of which has its own index registers, IDH, IDL0 and IDL1. The banks of index registers can be switched by setting an appropriate value in SR0[2] (See SR0 for details). Normally, programmers can reserve an index register pair, IDH and IDL0 (or IDL1), for software stack operations.

## LINK REGISTERS: ILX, ILH AND ILL

The link registers are specially designed for link-and-branch instructions (See LNK and LRET instructions in the instruction sections for details). When an LNK instruction is executed, the current PC[19:0] is saved into ILX, ILH and ILL registers, i.e., PC[19:16] into ILX[3:0], PC[15:8] into ILH [7:0], and PC[7:0] into ILL[7:0], respectively. When an LRET instruction is executed, the return PC value is recovered from ILX, ILH, and ILL, i.e., ILX[3:0] into PC[19:16], ILH[7:0] into PC[15:8] and ILL[7:0] into PC[7:0], respectively. These registers are used to access program memory by LDC/LDC+ instructions. When an LDC or LDC+ instruction is executed, the (code) data residing at the program address specified by ILX:ILH:ILL will be read into TBH:TBL. LDC+ also increments ILL after accessing the program memory.

There is a special core input pin signal, nP64KW, which is reserved for indicating that the program memory address space is only 64 K word. By grounding the signal pin to zero, the upper 4 bits of PC, PC[19:16], are deactivated and therefore the upper 4 bits, PA[19:16], of the program memory address signals from CalmRISC core are also deactivated. By doing so, the power consumption due to manipulating the upper 4 bits of PC can be totally eliminated (See the core pin description section for details). From the programmer's standpoint, when nP64KW is tied to the ground level, PC[19:16] is *not* saved into ILX for LNK instructions and ILX is *not* read back into PC[19:16] for LRET instructions. Therefore, ILX is totally unused for LNK and LRET instructions when nP64KW = 0.

#### **STATUS REGISTER 0: SR0**

SR0 is mainly reserved for system control functions and each bit of SR0 has its own dedicated function.

| Flag Name | Bit | Description                                     |  |

|-----------|-----|-------------------------------------------------|--|

| eid       | 0   | Data memory page selection in direct addressing |  |

| ie        | 1   | Global interrupt enable                         |  |

| idb       | 2   | Index register banking selection                |  |

| grb[1:0]  | 4,3 | GPR bank selection                              |  |

| exe       | 5   | Stack overflow/underflow exception enable       |  |

| ie0       | 6   | Interrupt 0 enable                              |  |

| ie1       | 7   | Interrupt 1 enable                              |  |

SR0[0] (or eid) selects which page index is **to be** used in direct addressing. If eid = 0, then page 0 (page index = 0) is used. Otherwise (eid = 1), IDH of the current index register bank is used for page index. SR0[1] (or ie) is the global interrupt enable flag. As explained in the interrupt/exception section, CalmRISC has 3 interrupt sources (non-maskable interrupt, interrupt 0, and interrupt 1) and 1 stack exception. Both interrupt 0 and interrupt 1 are masked by setting SR0[1] to 0 (i.e., ie = 0). When an interrupt is serviced, the global interrupt enable flag ie is automatically cleared. The execution of an IRET instruction (return from an interrupt service routine) automatically sets ie = 1. SR0[2] (or idb) and SR0[4:3] (or grb[1:0]) selects select an appropriate bank for index registers and GPR's, respectively(,) as shown below:

Figure 3-1. Bank Selection by Setting of GRB Bits and IDB Bit

SR0[5] (or exe) enables the stack exception, that is, the stack overflow/underflow exception. If exe = 0, the stack exception is disabled. The stack exception can be used for program debugging in the software development stage. SR0[6] (or ie0) and SR0[7] (or ie1) are enabled, by setting them to 1. Even though ie0 er are ie1 are enabled, the interrupts are ignored (not serviced) if the global interrupt enable flag ie is set to 0.

#### **STATUS REGISTER 1: SR1**

SR1 is the register for status flags such as the ALU execution flag and stack full flag.

| Flag Name | Bit     | Description     |

|-----------|---------|-----------------|

| С         | 0       | Carry flag      |

| V         | 1       | Overflow flag   |

| Z         | 2       | Zero flag       |

| N         | 3       | Negative flag   |

| SF        | 4       | Stack Full flag |

| -         | 5, 6, 7 | Reserved        |

SR1[0] (or C) is the carry flag of ALU executions. SR1[1] (or V) is the overflow flag of ALU executions. It is set to 1 if and only if the carry-in into the 8-th bit position of addition/subtraction differs from the carry-out from the 8-th bit position. SR1[2] (or Z) is the zero flag, which is set to 1 if and only if the ALU result is zero. SR1[3] (or N) is the negative flag. Basically, the most significant bit (MSB) of ALU results becomes the N flag. Note a load instruction into a GPR is considered an ALU instruction. However, if an ALU instruction touches the overflow flag (V) like ADD, SUB, CP, *etc*, N flag is updated as exclusive-OR of V and the MSB of the ALU result. This implies that even if an ALU operation results in overflow, N flag is still valid. SR1[4] (or SF) is the stack overflow flag. It is set when the hardware stack is overflowed or underflowed. Programmers can check if the hardware stack has any abnormalities by checking the stack exception or testing if SF is set (See the hardware stack section for more details).

NOTE: When an interrupt occurs SR0 and SR1 are not saved by hardware, so the SR1 register values must be saved by software.

# **4** CONTROL REGISTERS

## **OVERVIEW**

To support the control of peripheral hardware, the addresses for peripheral control registers are memory-mapped to page 0 of the RAM. Memory mapping lets you use a mnemonic as the operand of an instruction in place of the specific memory location.

In this section, detailed descriptions of the S3CB018/FB018 control registers are presented in an easy-to-read format.

You can use this section as a quick-reference source when you write application programs.

This memory area can be accessed with the whole method of data memory access.

- If SR0 bit 0 is "0", then the accessed register area is always page 0.

- If SR0 bit 0 is "1", then the accessed register page is controlled by the proper IDH register's value.

So if you want to access the memory map area, clear the SR0.0 and use the direct addressing mode. This method is used for most cases.

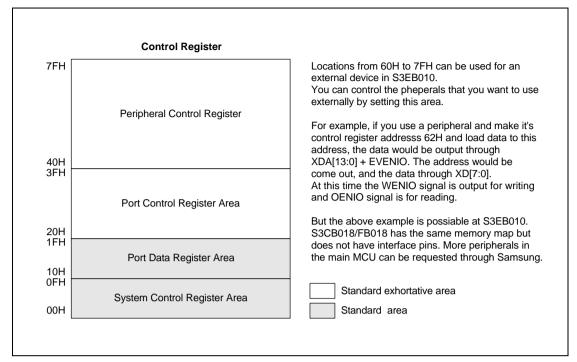

This control register is divided into four areas. Here, the system control register area is the same in every device.

Figure 4-1. Memory Map Areas

| Register Name                   | Mnemonic                  | Decimal | Hex | Reset | R/W |

|---------------------------------|---------------------------|---------|-----|-------|-----|

| Ŭ                               | cations 14H-1FH are not i | mapped  |     |       |     |

| Port 3 data register            | P3                        | 19      | 13H | 00H   | R/W |

| Port 2 data register            | P2                        | 18      | 12H | 00H   | R/W |

| Port 1 data register            | P1                        | 17      | 11H | 00H   | R/W |

| Port 0 data register            | P0                        | 16      | 10H | 00H   | R/W |

| Watchdog timer control register | WDTCON                    | 15      | 0FH | 00H   | R/W |

| Watchdog timer enable register  | WDTEN                     | 14      | 0EH | A5H   | R/W |

| Basic timer counter             | BTCNT                     | 13      | 0DH | 00H   | R   |

| Basic timer control register    | BTCON                     | 12      | 0CH | 70H   | R/W |

| Interrupt ID register 1         | IIR1                      | 11      | 0BH | -     | R/W |

| Interrupt priority register 1   | IPR1                      | 10      | 0AH | -     | R/W |

| Interrupt mask register 1       | IMR1                      | 9       | 09H | 00H   | R/W |

| Interrupt request register 1    | IRQ1                      | 8       | 08H | 00H   | R   |

| Interrupt ID register 0         | IIR0                      | 7       | 07H | -     | R/W |

| Interrupt priority register 0   | IPR0                      | 6       | 06H | -     | R/W |

| Interrupt mask register 0       | IMR0                      | 5       | 05H | 00H   | R/W |

| Interrupt request register 0    | IRQ0                      | 4       | 04H | 00H   | R   |

| Oscillator control register     | OSCCON                    | 3       | 03H | 00H   | R/W |

| Power control register          | PCON                      | 2       | 02H | 04H   | R/W |

| Loc                             | cations 00H-01H are not r | mapped  |     |       |     |

## Table 4-1. Registers

NOTES:

1. '-' means undefined.

2. If you want to clear the bit of IRQx, then write the number which you want to clear to IIRx. For example, when clear IRQ0.4 then LD Rx, #04H and LD IIRQ, Rx.

| Tabi                              | e 4-1. Registers (cont | inueu)        |             |       |     |

|-----------------------------------|------------------------|---------------|-------------|-------|-----|

| Register Name                     | Mnemonic               | Decimal       | Hex         | Reset | R/W |

| Locations 51H-7FH are no          | t mapped (reserved for | extra periphe | rals extern | ally) |     |

| Watch timer control register      | WTCON                  | 80            | 50H         | 00H   | R/W |

| ADDA data register low byte       | ADDATAL                | 79            | 4FH         | 00H   | R/W |

| ADDA data register high byte      | ADDATAH                | 78            | 4EH         | 00H   | R/W |

| Lo                                | cations 4DH is not map | oped          |             |       |     |

| ADDASIO control register          | ADDACON                | 76            | 4CH         | 00H   | R/W |

| Lo                                | cations 4BH is not map | oped          |             |       |     |

| Serial I/O data register          | SIODATA                | 74            | 4AH         | 00H   | R/W |

| Serial I/O pre-scale register     | SIOPS                  | 73            | 49H         | 00H   | R/W |

| Serial I/O control register       | SIOCON                 | 72            | 48H         | 00H   | R/W |

| L                                 | ocation 47H is not map | ped           |             |       |     |

| Timer B counter                   | TBCNT                  | 70            | 46H         | -     | R   |

| Timer B data register             | TBDATA                 | 69            | 45H         | 00H   | R/W |

| Timer B control register          | TBCON                  | 68            | 44H         | 00H   | R/W |

| L                                 | ocation 43H is not map | ped           |             |       |     |

| Timer A counter                   | TACNT                  | 66            | 42H         | -     | R   |

| Timer A data register             | TADATA                 | 65            | 41H         | 00H   | R/W |

| Timer A control register          | TACON                  | 64            | 40H         | 00H   | R/W |

| Locat                             | ions 2DH-3FH are not   | mapped        |             |       |     |

| Port 3 control register           | P3CON                  | 44            | 2CH         | 00H   | R/W |

| Lo                                | ocation 2BH is not map | ped           |             |       |     |

| Port 2 interrupt control register | P2INT                  | 42            | 2AH         | 00H   | R/W |

| Port 2 control register low       | P2CONL                 | 41            | 29H         | 00H   | R/W |

| Port 2 control register high      | P2CONH                 | 40            | 28H         | 00H   | R/W |

| Locat                             | ions 25H-27H are not r | mapped        |             |       |     |

| Port 1 control register           | P1CON                  | 36            | 24H         | 00H   | R/W |

| Locat                             | ions 22H-23H are not r | mapped        |             |       |     |

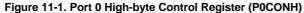

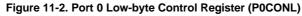

| Port 0 control register low       | P0CONL                 | 33            | 21H         | 00H   | R/W |

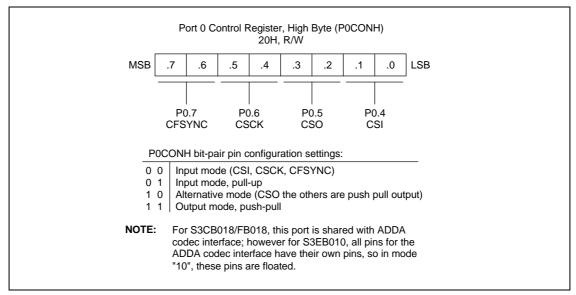

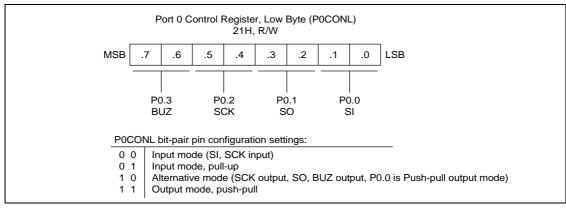

| Port 0 control register high      | P0CONH                 | 32            | 20H         | 00H   | R/W |

## Table 4-1. Registers (continued)

# 5 HARDWARE STACK

# OVERVIEW

The hardware stack in CalmRISC has two usages:

- To save and restore the return PC[19:0] on LCALL, CALLS, RET, and IRET instructions.

- To use as temporary storage space for registers on PUSH and POP instructions.

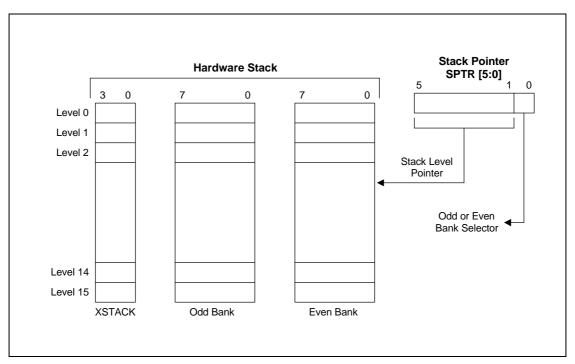

When PC[19:0] is saved into or restored from the hardware stack, the access should be 20 bits wide. On the other hand, when a register is pushed into or popped from the hardware stack, the access should be 8 bits wide. Hence, to maximize the efficiency of the stack usage, the hardware stack is divided into 3 parts: the extended stack bank (XSTACK, 4-bits wide), the odd bank (8-bits wide) and the even bank (8-bits wide).

Figure 5-1. Hardware Stack

5-1

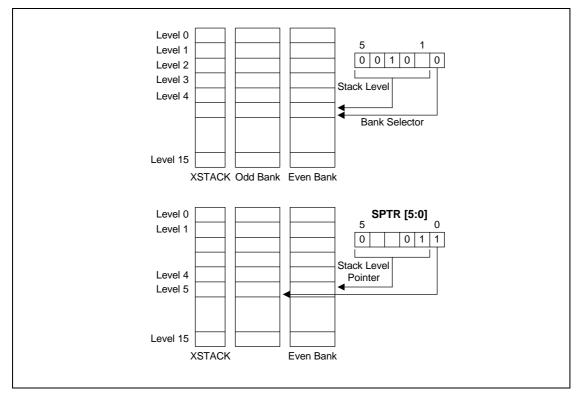

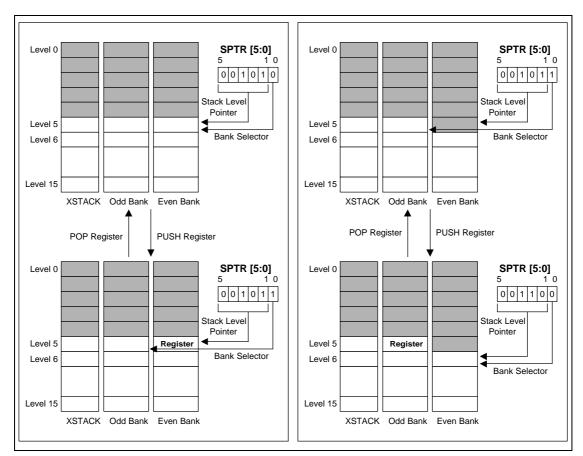

The stack pointer, called sptr[5:0], points to the top of the stack (TOS). The upper 5 bits of the stack pointer, sptr[5:1], points to the stack level, where either PC[19:0] or a register is saved. For example, if sptr[5:1] is 5H or TOS is 5, then level 5 of XSTACK is empty and either level 5 of the odd bank or level 5 of the even bank is empty. In fact, sptr[0], the stack bank selection bit, indicates which bank(s) is empty. If sptr[0] = 0, both level 5 of the even and the odd banks are empty. On the other hand, if sptr[0] = 1, level 5 of the odd bank is empty, but level 5 of the even bank is occupied. This situation is well illustrated in the figure below.

Figure 5-2. Even and Odd Bank Selection Example

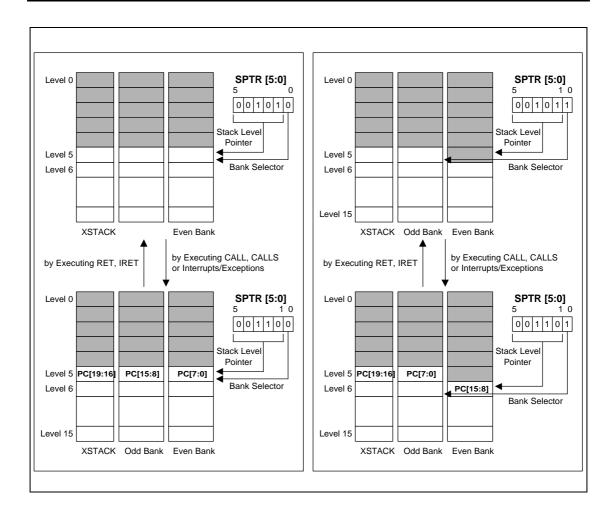

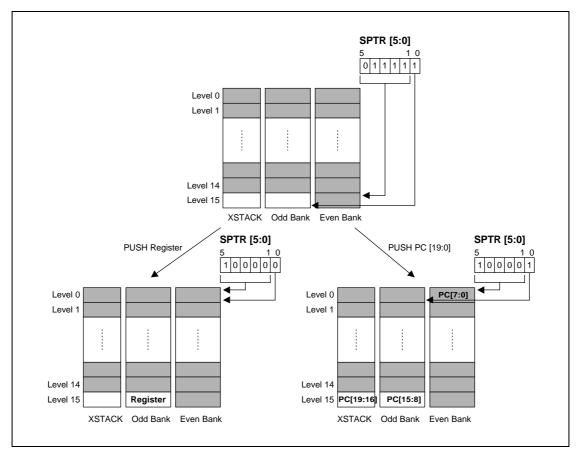

As can be seen in the above example, sptr[5:1] is used as the hardware stack pointer when PC[19:0] is pushed or popped and sptr[5:0] as the hardware stack pointer when a register is pushed or popped. Note that XSTACK is used only for storing and retrieving PC[19:16]. Let us consider the cases where PC[19:0] is pushed into the hardware stack (by executing LCALL/CALLS instructions or by interrupts/exceptions being served) or is retrieved from the hardware stack (by executing RET/IRET instructions). Regardless of the stack bank selection bit (sptr[0]), TOS of the even bank and the odd bank store or return PC[7:0] or PC[15:8], respectively. This is illustrated in the following figures.

As can be seen in the figures, when stack operations with PC[19:0] are performed, the stack level pointer sptr[5:1] (*not* sptr[5:0]) is either incremented by 1 (when PC[19:0] is pushed into the stack) or decremented by 1 (when PC[19:0] is popped from the stack). The stack bank selection bit (sptr[0]) is unchanged. If a CalmRISC core input signal *nP64KW* is 0, signifying that only PC[15:0] is meaningful, then any access to XSTACK is totally deactivated from the stack operations with PC. Therefore, XSTACK has no meaning when the input pin signal, *nP64KW*, is tied to 0. In that case, XSTACK does not have to even exist. As a matter of fact, XSTACK is not included in CalmRISC core itself, and it is interfaced through some specially reserved core pin signals (*nPUSH, nSTACK, XHSI[3:0], XSHO[3:0]*), if the program address space is more than 64 K words (See the core pin signal section for details).

A similar argument can be made with regards to stack operations with registers. A stack pointer, called sptr[5:0], points to the top of the stack (TOS). The only difference is that the data written into or read from the stack are a byte. Hence, the even bank and the odd bank are accessed alternately as shown below.

Figure 5-4. Stack Operation with Registers

When the bank selection bit (sptr[0]) is 0, the register is pushed into the even bank and the bank selection bit is set to 1. In this case, the stack level pointer is unchanged. When the bank selection bit (sptr[0]) is 1, then the register is pushed into the odd bank, the bank selection bit is set to 0, and the stack level pointer is incremented by 1. Unlike the push operations of PC[19:0], no data are written into XSTACK in the register push operations. This is illustrated in the example figures. When a register is pushed into the stack, sptr[5:0] is incremented by 1 (*not* the stack level pointer sptr[5:1]). The register pop operations are the reverse processes of the register push operations. When a register is popped out of the stack, sptr[5:0] is decremented by 1 (*not* the stack level pointer sptr[5:1]).

Hardware stack overflows/underflows when the MSB of the stack level pointer, sptr[5], is 1. This is obvious from the fact that the hardware stack has only 16 levels and the following relationship holds for the stack level pointer in a normal case.

Suppose the stack level pointer sptr[5:1] = 15 (or 01111B in binary format) and the bank selection bit sptr[0] = 1. Here if either PC[19:0] or a register is pushed, the stack level pointer is incremented by 1. Therefore, sptr[5:1] = 16 (or 10000B in binary format) and sptr[5] = 1, which imply that the stack is overflowed. The situation is depicted in the following.

Figure 5-5. Stack Overflow

The first overflow happens due to a register push operation. As explained earlier, a register push operation increments sptr[5:0] (not sptr[5:1]), which results in sptr[5] = 1, sptr[4:1] = 0 and sptr[0] = 0. As indicated by sptr[5] = 1, an overflow happens. Note that this overflow does not overwrite any data in the stack. On the other hand, when PC[19:0] is pushed, sptr[5:1] is incremented by 1 instead of sptr[5:0], and as expected, an overflow results. Unlike the first overflow, PC[7:0] is pushed into level 0 of the even bank and the data that have been there before the push operation are *overwritten*. A similar argument can be made about stack underflows. Note that any stack operation, which causes the stack to overflow or underflow, does not necessarily mean that any data in the stack are lost, as is observed in the first example.

In SR1, there is a status flag, SF (Stack Full Flag), which is exactly the same as sptr[5]. In other words, the value of sptr[5] can be checked by reading SF (or SR1[4]). SF is set to 1 if there is an stack overflow/underflow. If POP operation is executed after overflow, SF is cleared to 0. So programmers cannot tell whether there was a stack overflow/underflow just by reading SF. For example, if a program pushes a register 64 times in a row, sptr[5:0] is exactly the same as sptr[5:0] before the push sequence. Therefore, special attention should be paid.

Another mechanism to detect a stack overflow/underflow is through a stack exception. A stack exception happens only when the execution of any stack access instruction results in SF = 1 (or sptr[5] = 1). Suppose a register push operation makes SF = 1 (the SF value before the push operation does not matter). Then the stack exception due to the push operation is immediately generated and served, if the stack exception enable flag (exe of SR0) is 1. If the stack exception enable flag is 0, then the generated interrupt is not served but pending. Sometime later when the stack exception enable flag is set to 1, the pending exception request is served even if SF = 0. More details are available in the stack exception section.

## 6 EXCEPTIONS

### **OVERVIEW**

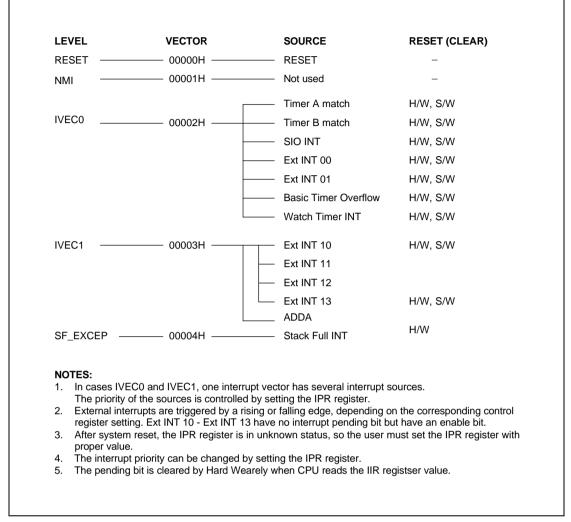

Exceptions in CalmRISC are listed in the table below. Exception handling routines, residing at the given addresses in the table, are invoked when the corresponding exception occurs. The starting address of each exception routine is specified by concatenating 0H (leading 4 bits of 0) and the 16-bit data in the exception vector listed in the table. For example, the interrupt service routine for IRQ[0] starts from 0H:PM[00002H]. Note that ":" means concatenation and PM[\*] stands for the 16-bit content at the address \* of the program memory. Aside from the exception due to reset release, the current PC is pushed in the stack on an exception. When an exception is executed due to IRQ[1:0]/IEXP, the global interrupt enable flag, bit (SR0[1]), is set to 0, and ie is set to 1 when IRET or an instruction that explicitly sets ie is executed.

| Name   | Address | Priority | Description                                                         |

|--------|---------|----------|---------------------------------------------------------------------|

| Reset  | 00000H  | 1 st     | Exception due to rest release.                                      |

| -      | 00001H  | _        | Reserved.                                                           |

| IRQ[0] | 00002H  | 3 rd     | Exception due to <i>nIRQ[0]</i> signal. Maskable by setting ie/ie0. |

| IRQ[1] | 00003H  | 4 th     | Exception due to nIRQ[1] signal. Maskable by setting ie/ie1.        |

| IEXP   | 00004H  | 2 nd     | Exception due to stack full. Maskable by setting exe.               |

| -      | 00005H  | -        | Reserved.                                                           |

| -      | 00006H  | _        | Reserved.                                                           |

| -      | 00007H  | -        | Reserved.                                                           |

### Table 6-1. Exceptions

**NOTE:** Break mode due to BKREQ has a higher priority than all the exceptions above. That is, when BKREQ is active, even the exception due to reset release is not executed.

### HARDWARE RESET

When Hardware Reset is active (the reset input signal pin nRES = 0), the control pins in the CalmRISC core are initialized to be disabled, and SR0 and sptr (the hardware stack pointer) are initialized to be 0. Additionally, the interrupt sensing block is cleared. When Hardware Reset is released (nRES = 1), the reset exception is executed by loading the JP instruction in IR (Instruction Register) and 0h:0000h in PC. Therefore, when Hardware Reset is released, the "JP {0h:PM[00000h]}" instruction is executed. When the reset exception is executed, a core output signal *nEXPACK* is generated to acknowledge the exception.

### **IRQ[0] EXCEPTION (LEVEL-SENSITIVE)**

When a core input signal *nIRQ[0]* is low, SR0[6] (ie0) is high, and SR0[1] (ie) is high and IRQ[0] exception is generated; this will load the CALL instruction in IR (Instruction Register) and 0h:0002h in PC. Therefore, on an IRQ[0] exception, the "CALL {0h:PM[00002h]}" instruction is executed. When the IRQ[0] exception is executed, SR0[1] (ie) is set to 0 and a core output signal *nEXPACK* is generated to acknowledge the exception.

### **IRQ[1] EXCEPTION (LEVEL-SENSITIVE)**

When a core input signal *nIRQ[1]* is low, SR0[7] (ie1) is high, and SR0[1] (ie) is high and IRQ[1] exception is generated; this will load the CALL instruction in IR (Instruction Register) and 0h:0003h in PC. Therefore, on an IRQ[1] exception, the "CALL {0h:PM[00003h]}" instruction is executed. When the IRQ[1] exception is executed, SR0[1] (ie) is set to 0 and a core output signal *nEXPACK* is generated to acknowledge the exception.

### HARDWARE STACK FULL EXCEPTION

A Stack Full exception occurs when a stack operation is performed and as a result of the stack operation sptr[5] (SF) is set to 1. If the stack exception enable bit, exe (SR0[5]), is 1, the Stack Full exception is served. One exception to this rule is when nNMI causes a stack operation that sets sptr[5] (SF), since it has higher priority.

Handling a Stack Full exception may cause another Stack Full exception. In this case, the new exception is ignored. On a Stack Full exception, the CALL instruction is loaded in IR (Instruction Register) and 0h:0004h in PC. Therefore, when the Stack Full exception is activated, the "CALL {0h:PM[00004h]}" instruction is executed. When the exception is executed, SR0[1] (ie) is set to 0, and a core output signal *nEXPACK* is generated to acknowledge the exception.

### **BREAK EXCEPTION**

Break exception is reserved only for an in-circuit debugger. When a core input signal, *BKREQ*, is high, the CalmRISC core is halted or entered in the break mode, until *BKREQ* is deactivated. Another way to drive the CalmRISC core into the break mode is by executing a break instruction, BREAK. When BREAK is fetched, it is decoded in the fetch cycle (IF stage) and the CalmRISC core output signal *nBKACK* is generated in the second cycle (ID/MEM stage). An in-circuit debugger makes *BKREQ* active by monitoring whether *nBKACK* is active or not. BREAK instruction is exactly the same as the NOP (no operation) instruction except that it does not increase the program counter. It activates nBKACK in the second cycle (or ID/MEM stage of the pipeline). There, once BREAK is encountered in the program execution, it falls into a deadlock. BREAK instruction is reserved for in-circuit debuggers only, so it should not be used in user programs.

### **EXCEPTIONS (or INTERRUPTS)**

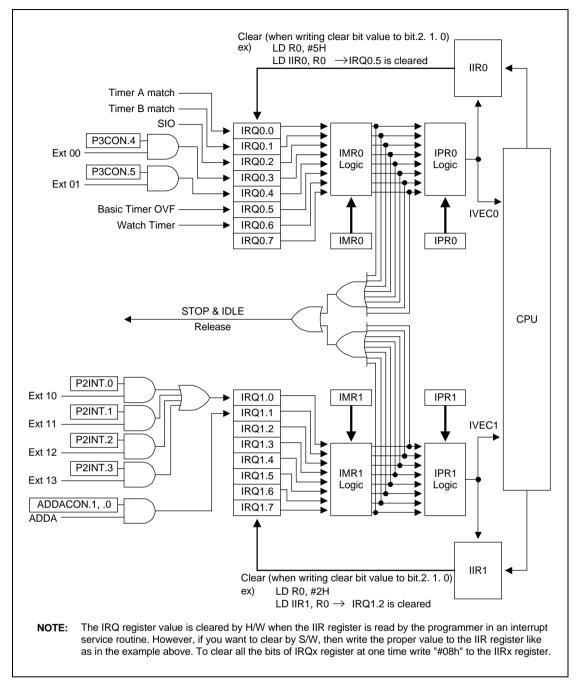

Figure 6-1. Interrupt Structure

Figure 6-2. Interrupt Block Diagram

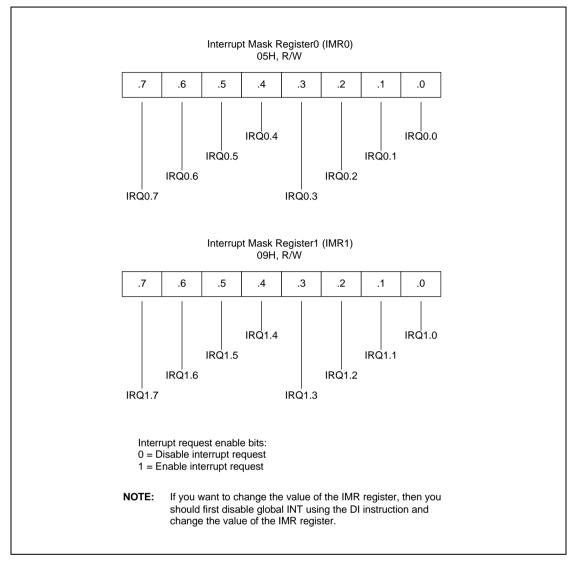

### INTERRUPT MASK REGISTERS

Figure 6-3. Interrupt Mask Register

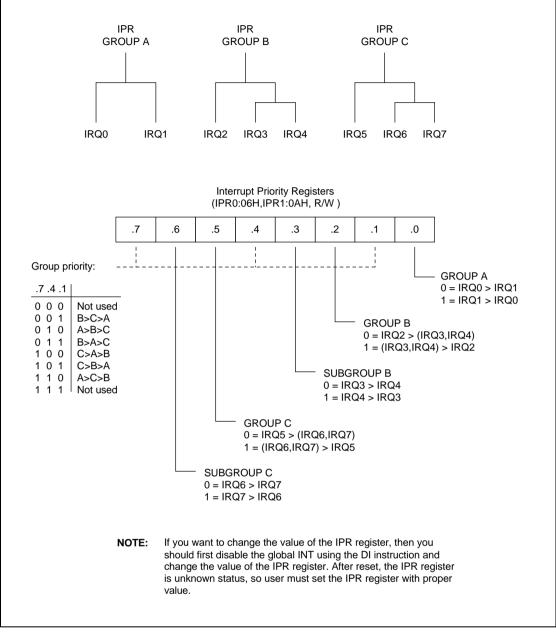

### INTERRUPT PRIORITY REGISTER

Figure 6-4. Interrupt Priority Register

### PROGRAMMING TIP —Interrupt Programming Tip 1

Jumped from vector 2

|          | PUSH                                                 | SR1                                                                                                           |

|----------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|          | PUSH<br>LD<br>CP<br>JR<br>CP<br>JR<br>CP<br>JP<br>JP | R0<br>R0, IIR0<br>R0, #03h<br>ULE, LTE03<br>R0, #05h<br>ULE, LTE05<br>R0, #06h<br>EQ, IRQ6_srv<br>T, IRQ7_srv |

| LTE05    | CP<br>JP<br>JP                                       | R0, #04<br>EQ, IRQ4_srv<br>T, IRQ5_srv                                                                        |

| LTE03    | CP<br>JR<br>CP<br>JP<br>JP                           | R0, #01<br>ULE, LTE01<br>R0, #02<br>EQ, IRQ2_srv<br>T, IRQ3_srv                                               |

| LTE01    | GP<br>JP<br>JP                                       | R0, #00h<br>EQ, IRQ0_srv<br>T, IRQ1_srv                                                                       |

| IRQ0_srv | $\rightarrow$ service for IRQ0                       |                                                                                                               |

|          | POP<br>POP<br>IRET                                   | R0<br>SR1                                                                                                     |

| IRQ1_srv | $\rightarrow$ service f                              | or IRQ1                                                                                                       |

|          | •<br>POP<br>POP<br>IRET<br>•                         | R0<br>SR1                                                                                                     |

| IRQ7_srv | $\rightarrow$ service f                              | or IRQ7                                                                                                       |

|          | •<br>POP<br>POP<br>IRET                              | R0<br>SR1                                                                                                     |

**NOTE:** If the SR0 register is changed in the interrupt service routine, then the SR0 register must be pushed and popped in the interrupt service routine.

### PROGRAMMING TIP —Interrupt Programming Tip 2

| oumped non |                                                                                        |                                                                                              |

|------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|            | PUSH<br>PUSH<br>PUSH<br>LD                                                             | SR1<br>R0<br>R1<br>R0, IIRx                                                                  |

|            | SL<br>LD<br>ADD<br>PUSH<br>PUSH<br>RET                                                 | R0<br>R1, < TBL_INTx<br>R0, > TBL_INTx<br>R1<br>R0                                           |

| TBL_INTx   | LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP<br>LJP                                   | IRQ0_svr<br>IRQ1_svr<br>IRQ2_svr<br>IRQ3_svr<br>IRQ4_svr<br>IRQ5_svr<br>IRQ6_svr<br>IRQ7_svr |

| IRQ0_srv   | <ul> <li>→ service for</li> <li>POP</li> <li>POP</li> <li>POP</li> <li>IRET</li> </ul> | r IRQ0<br>R1<br>R0<br>SR1                                                                    |

| IRQ1_srv   | $\rightarrow$ service fo                                                               | or IRQ1                                                                                      |

|            | POP<br>POP<br>POP<br>IRET                                                              | R1<br>R0<br>SR1                                                                              |

| IRQ7_srv   | $\rightarrow$ service for                                                              | or IRQ7                                                                                      |

|            | POP<br>POP<br>POP<br>IRET                                                              | R1<br>R0<br>SR1                                                                              |

### NOTES:

1. If the SR0 register is changed in the interrupt service routine, then the SR0 register must be pushed and popped in the interrupt service routine.

2. The above example assumes that the ROM size is less than 64K word and all the LJP instructions in the jump table (TBL-INTx) is in the same page.

### **7** COPROCESSOR INTERFACE

### **OVERVIEW**

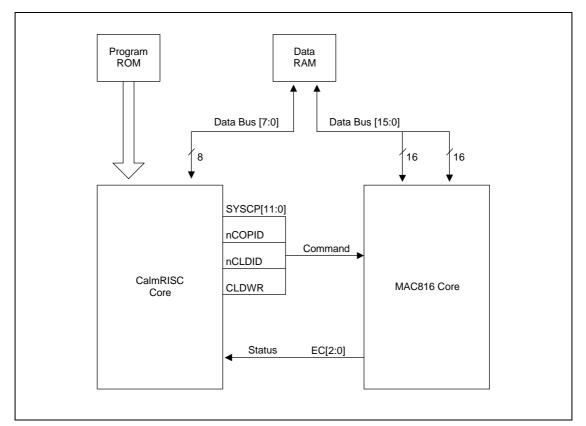

CalmRISC supports an efficient and seamless interface with coprocessors. By integrating a MAC (multiply and accumulate) DSP coprocessor engine with the CalmRISC core, not only the microcontroller functions but also complex digital signal processing algorithms can be implemented in a single development platform (or MDS). CalmRISC has a set of dedicated signal pins, through which data/command/status are exchanged to and from a coprocessor. Depicted below are the coprocessor signal pins and the interface between two processors.

Figure 7-1. Coprocessor Interface Diagram

As shown in the coprocessor interface diagram above, the coprocessor interface signals of CalmRISC are: SYSCP[11:0], nCLDID, nCLDWR, and EC[2:0]. The data are exchanged through data buses, DI[7:0] and D0[7:0]. A command is issued from CalmRISC to a coprocessor through SYSCP[11:0] in COP instructions. The status of a coprocessor can be sent back to CalmRISC through EC[2:0] and these flags can be checked in the condition codes of branch instructions. The coprocessor instructions are listed in the following table

| Mnemonic  | Op 1    | Op 2  | Description                                      |

|-----------|---------|-------|--------------------------------------------------|

| COP       | #imm:12 | -     | Coprocessor operation                            |

| CLD       | GPR     | imm:8 | Data transfer from coprocessor into GPR          |

| CLD       | imm:8   | GPR   | Data transfer of GPR to coprocessor              |

| JP(or JR) | EC2-EC0 | label | Conditional branch with coprocessor status flags |

| CALL      |         |       |                                                  |

| LNK       |         |       |                                                  |

| Table 7-1 | Coprocessor | instructions |

|-----------|-------------|--------------|

|-----------|-------------|--------------|

The coprocessor of CalmRISC does not have its own program memory (i.e., it is a passive coprocessor) as shown in Figure 7 -1. In fact, the coprocessor instructions are fetched and decoded by CalmRISC, and CalmRISC issues the command to the coprocessor through interface signals. For example, if "COP #imm:12" instruction is fetched, then the 12-bit immediate value (imm:12) is loaded on *SYSCP[11:0]* signal with *nCOPID* active in ID/MEM stage, to request the coprocessor to perform the designated operation. The interpretation of the 12-bit immediate value is totally up to the coprocessor. By arranging the 12-bit immediate field, the instruction set of the coprocessor is determined. In other words, CalmRISC only provides a set of generic coprocessor instructions, and its installation to a specific coprocessor instruction set can differ from one coprocessor to another. CLD Write instructions ("CLD imm:8, GPR") put the content of a GPR register of CalmRISC on the data bus (*DO[7:0]*) and issue the address(imm:8) of the coprocessor internal register on *SYSCP[7:0]* with *nCLDID* active and *CLDWR* active. CLD Read instructions ("CLD GPR, imm:8" in Table 7-1) work similarly, except that the content of the coprocessor internal register addressed by the 8-bit immediate value is read into a GPR register through *DI[7:0]* with *nCLDID* active and *CLDWR* deactivated.

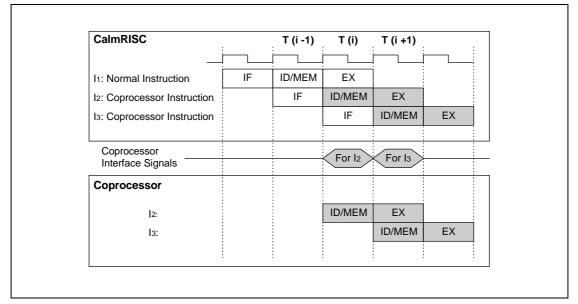

The timing diagram given below is a coprocessor instruction pipeline and shows when the coprocessor performs the required operations. Suppose  $I_2$  is a coprocessor instruction. First, it is fetched and decoded by CalmRISC (at t = T(i-1)). Once it is identified as a coprocessor instruction, CalmRISC indicates to the coprocessor the appropriate command through the coprocessor interface signals (at t = T(i)). Then the coprocessor performs the designated tasks at t = T(i) and t = T(i+1). Hence IF from CalmRISC and then ID/MEM and EX from the coprocessor constitute the pipeline for  $I_2$ . Similarly, if  $I_3$  is a coprocessor instruction, the coprocessor's ID/MEM and EX stages replace the corresponding stages of CalmRISC.

Figure 7-2. Coprocessor Instruction Pipeline

In a multi-processor system, the data transfer between processors is an important factor in determining the efficiency of the overall system. Suppose an input data stream is accepted by a processor, in order for the data to be shared by another processors. There should be some efficient mechanism to transfer the data to the processors. In CalmRISC, data transfers are accomplished through a single shared data memory. The shared data memory in a multi-processor has some inherent problems such as data hazards and deadlocks. However, the coprocessor in CalmRISC accesses the shared data memory only at the designated time at which time CalmRISC is guaranteed not to access the data memory, and therefore there is no contention over the shared data memory. Another advantage of the scheme is that the coprocessor can access the data memory in its own bandwidth.

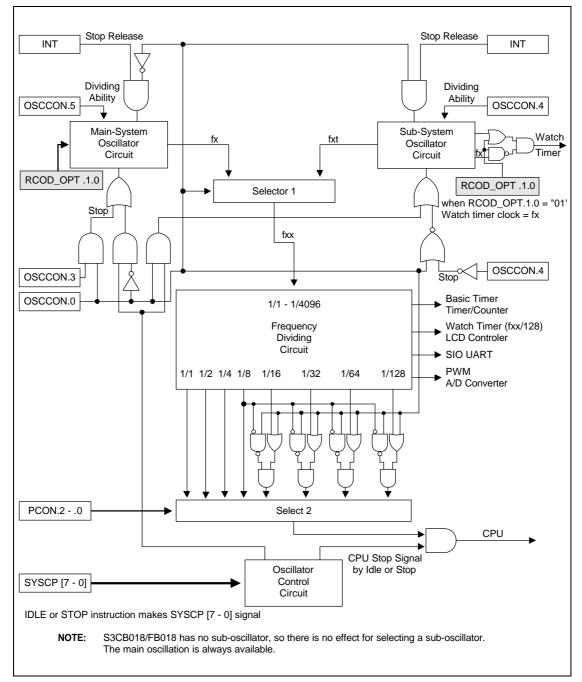

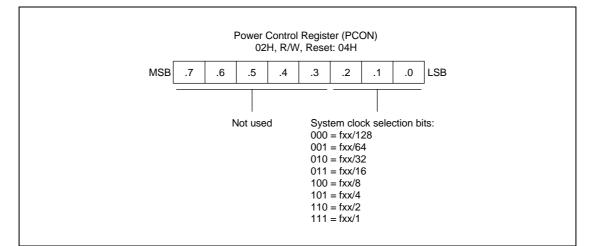

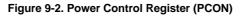

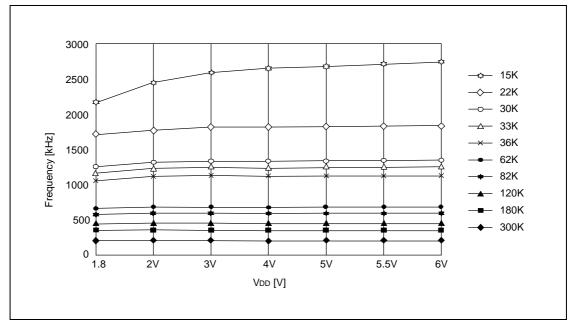

### 9 CLOCK CIRCUIT

### **OVERVIEW**

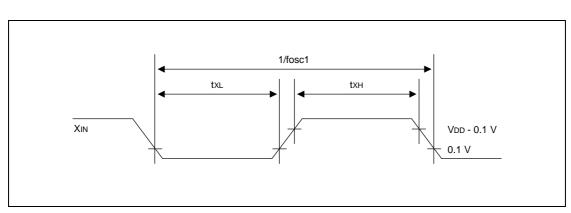

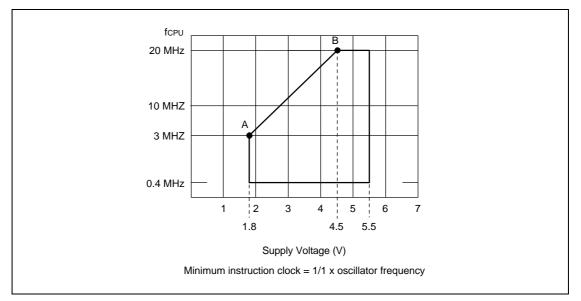

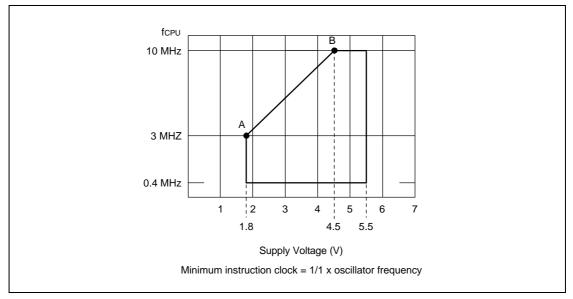

The clock frequency generated for the S3CB018/FB018 by an external crystal can range from 0.4MHz to 20MHz. The Xin and Xout pins connect the external oscillator or clock source to the on-chip clock circuit.

### SYSTEM CLOCK CIRCUIT

The system clock circuit has the following components:

- External crystal or ceramic resonator oscillation source (or an external clock source)

- Oscillator stop and wake-up functions

- Programmable frequency divider for the CPU clock (Fosc divided by 1, 2, 4, 8, 16, 32, 64, 128)

- System clock control register, PCON

Figure 9-1. System Clock Circuit Diagram

Figure 9-3. Oscillator Control Register (OSCCON)

# **10** RESET AND POWER-DOWN

### **OVERVIEW**

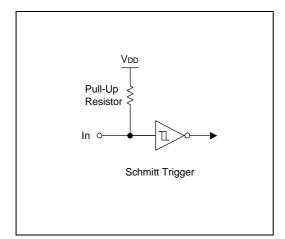

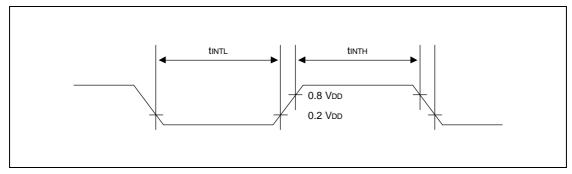

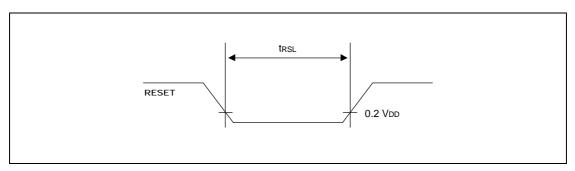

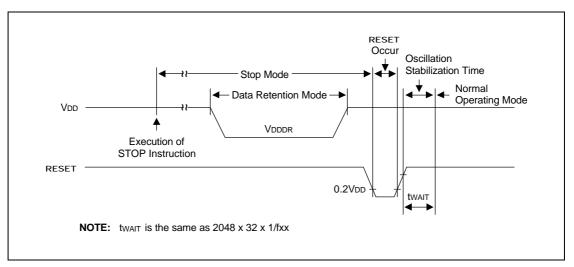

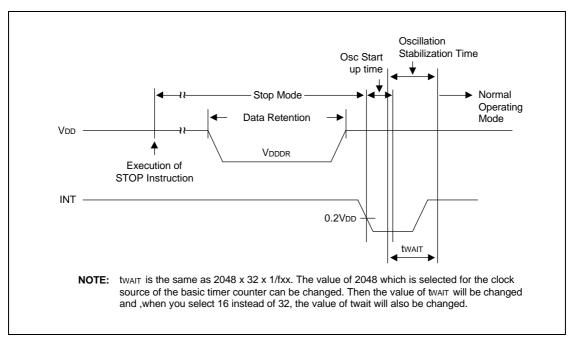

During a power-on reset, the voltage at  $V_{DD}$  goes to High level and the RESET pin is forced to Low level. The RESET signal is input through a Schmitt trigger circuit where it is then synchronized with the CPU clock. This procedure brings S3CB018/FB018 into a known operating status.

During the time required for the CPU clock oscillation to stabilize, the RESET pin must be held to low level for a minimum time, after the power supply comes within tolerance. This minimum time interval is identified in the electrical characteristics.

In summary, the following sequence of events occurs during a reset operation:

- All interrupts are disabled.

- The watchdog function (basic timer) is enabled.

- Ports are set to input mode except port 1 which is set to output mode.

- Peripheral control and data registers are disabled and reset to their default hardware values.

- The program counter (PC) is loaded with the program reset address in the ROM, 00000H.

- When the programmed oscillation stabilization time interval has elapsed, the instruction stored in ROM location 00000H is fetched and executed.

### NOTE

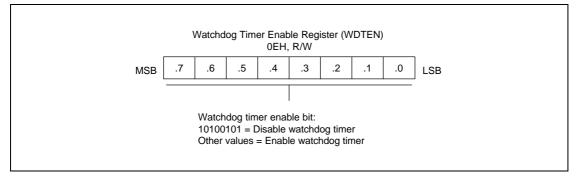

To program the duration of the oscillation stabilization interval, you make the appropriate settings to the basic timer control register, BTCON, before entering STOP mode. Also, if you do not want to use the basic timer watchdog function (which causes a system reset if a basic timer counter overflow occurs), you can disable it by writing '1010 0101b' to the WDTEN register.

# 11 I/O PORTS

Figure 11-3. Port 1 High-byte Control Register (P1CON)

Figure 11-5. Port 2 Low-byte Control Register (P2CONL)

Figure 11-6. Port 2 Interrupt Control Register (P2INT)

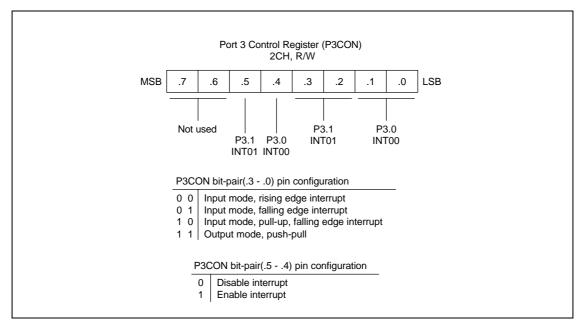

Figure 11-7. Port 3 Control Register (P3CON)

# 12 BASIC TIMER

### OVERVIEW

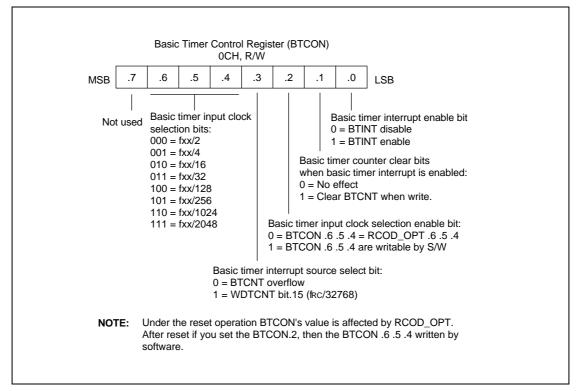

Figure 12-1. Basic Timer Control Register (BTCON)

### WATCHDOG TIMER

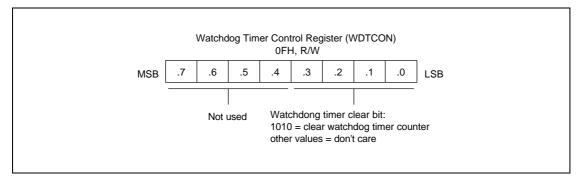

Figure 12-3. Watchdog Timer Enable Register (WDTEN)

### **BLOCK DIAGRAM**

Figure 12-4. Basic Timer & Watchdog Timer Functional Block Diagram

# 13 WATCH TIMER

### **OVERVIEW**

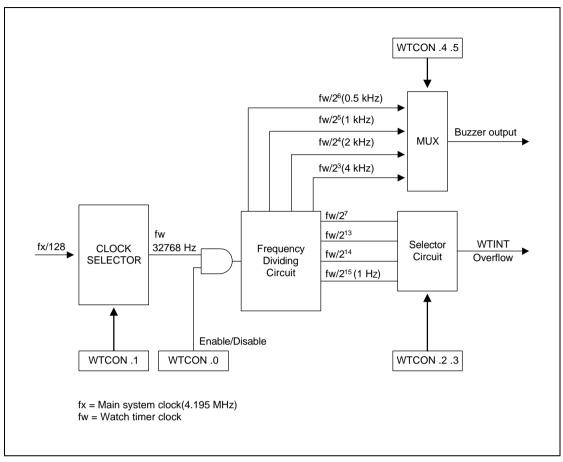

| Bit Name  | Values |   | Function                                                    | Address |

|-----------|--------|---|-------------------------------------------------------------|---------|

| WTCON.7   | _      |   | Not used                                                    | 50H     |

| WTCON.6   | -      |   | Not used                                                    |         |

| WTCON .54 | 0      | 0 | 0.5 kHz buzzer (BUZ) signal output                          |         |

|           | 0      | 1 | 1 kHz buzzer (BUZ) signal output                            |         |

|           | 1      | 0 | 2 kHz buzzer (BUZ) signal output                            |         |

|           | 1      | 1 | 4 kHz buzzer (BUZ) signal output                            |         |

| WTCON .32 | 0      | 0 | Set watch timer interrupt to 1S.                            |         |

|           | 0      | 1 | Set watch timer interrupt to 0.5S.                          |         |

|           | 1      | 0 | Set watch timer interrupt to 0.25S.                         |         |

|           | 1      | 1 | Set watch timer interrupt to 3.91mS.                        |         |

| WTCON.1   |        | 0 | Select (fx/128) as the watch timer clock                    |         |

|           | 1      |   | No effect, fx/128 is selected.                              |         |

| WTCON.0   | 0      |   | Stop watch timer counter; clear frequency dividing circuits |         |

|           |        | 1 | Run watch timer counter                                     |         |

### Table 13-1. Watch Timer Control Register (WTCON): 8-Bit R/W

NOTE: Main system clock frequency (fx) is assumed to be 4.195 MHz

### WATCH TIMER CIRCUIT DIAGRAM

Figure 13-1. Watch Timer Circuit Diagram

# **14** 16-BIT TIMER (8-BIT TIMER A & B)

### **OVERVIEW**

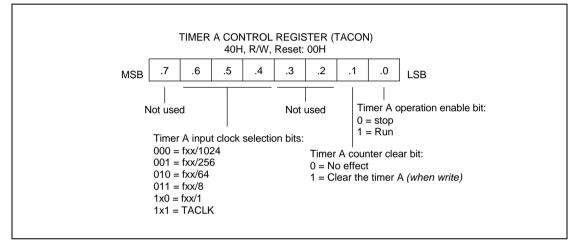

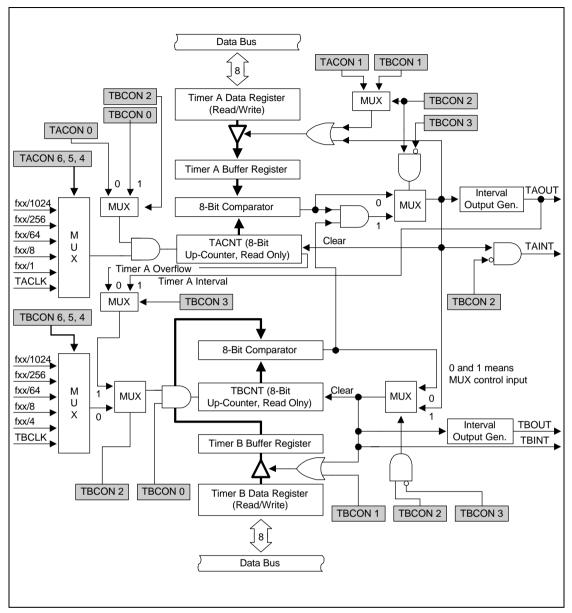

This 16-bit timer has two modes. One is 16-bit timer mode and the other is two 8-bit timer mode. When Bit 2 of TBCON is "0", it operates with the 16-bit timer. When it is "1", it operates with two 8-bit timers. When it operates with the 16-bit timer, the TBCNT's clock source can be selected by setting TBCON.3. If TBCON.3 is "0", the timer A's overflow would be TBCNT's clock source. If it is "1", the timer A's interval out would be TBCNT's clock source. The timer clock source can be selected by S/W.

Figure 14-1. Timer A Control Register (TACON)

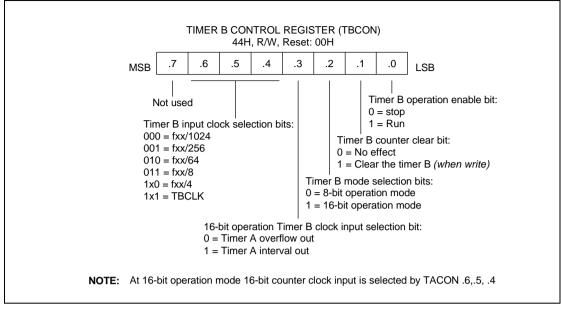

Figure 14-2. Timer B Control Register (TBCON)

Figure 14-3. Timer A, B Function Block Diagram

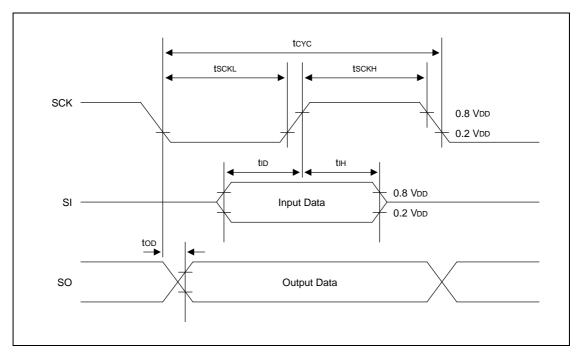

# 15 SERIAL I/O INTERFACE

### **OVERVIEW**

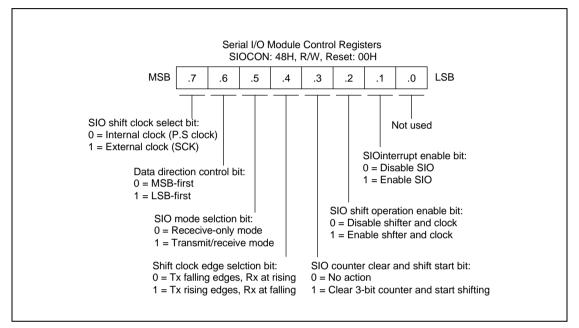

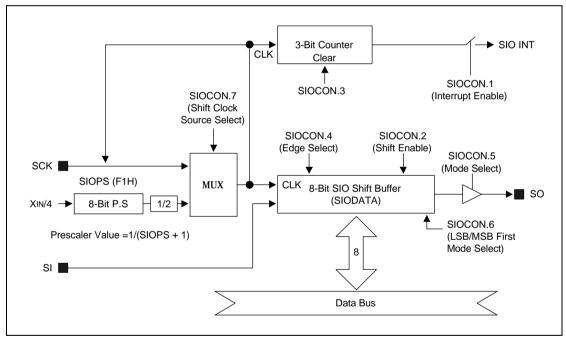

Figure 15-1. Serial I/O Module Control Registers (SIOCON)

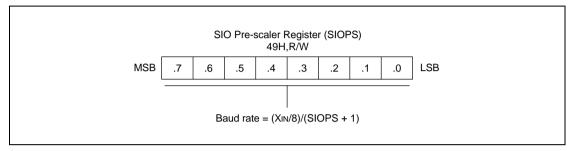

### SIO PRE-SCALER REGISTER (SIOPS)

The control register for serial I/O interface module, SIOPS, is located at 49H. The value stored in the SIO pre-scaler registers, SIOPS, lets you determine the SIO clock rate (baud rate) as follows:

### Baud rate = Input clock( X<sub>IN</sub>/8)/(Pre-scaler value + 1), or, SCLK input clock

where the input clock is  $X_{IN}$  / 4.

Figure 15-2. SIO Pre-scaler Register (SIOPS)

### **BLOCK DIAGRAM**

Figure 15-3. SIO Function Block Diagram

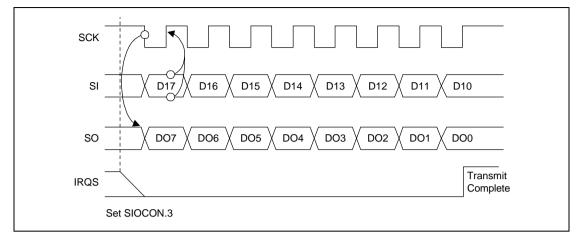

Figure 15-4. Serial I/O Timing in Transmit/Receive Mode(Tx at falling, SIOCON.4=0)

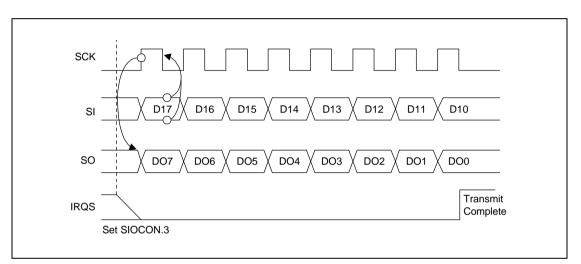

Figure 15-5. Serial I/O Timing in Transmit/Receive Mode(Tx at rising, SIOCON.4=1)

# 16 SERIAL I/O FOR ADC/DAC

### **OVERVIEW**

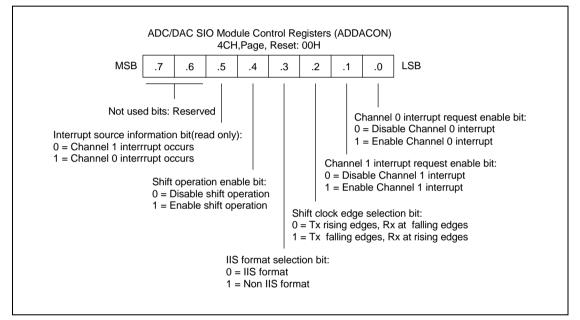

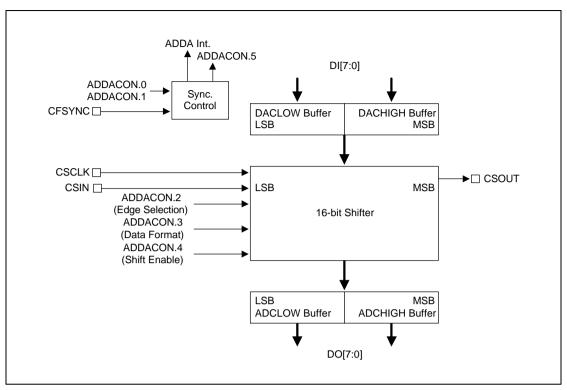

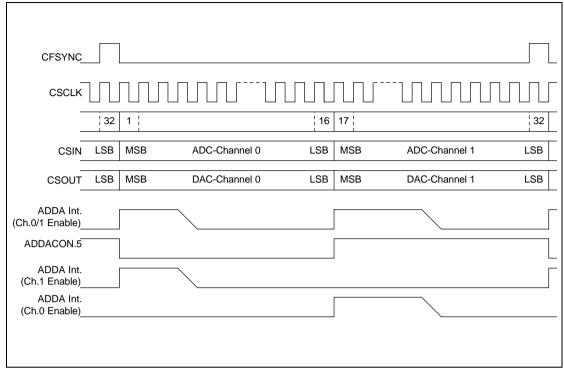

ADC/DAC Serial I/O module, ADDASIO, can interface with SM4 Master, 32 BPF mode of CS4216 <sup>(note)</sup>. The components of each ADDASIO function block are :

- 8-bit control register (ADDACON)

- 16-bit Data buffer (ADCHIGH, ADCLOW, DACHIGH, DACLOW)

- Serial data I/O pins (CSIN, CSOUT)

- Frame sync. pin (CFSYNC)

- External clock input/out pin (CSCLK)

The ADDASIO module can transmit or receive 2 channels of 16-bit serial data configured by its corresponding control register settings. The ADDASIO module operates with slave mode only.

### **Programming Procedure**

To program the ADDASIO modules, follow these basic steps:

- 1. Load an 8-bit value to the ADDACON control register to properly configure the ADDASIO module. (When using CS4216, ADDACON.3 must be cleared and CS4216 is configured to SM4 Master, 32 BPF mode).

- 2. Enable control (Channel 0/1 Enable, Shift Enable)

- 3. The ADDASIO interrupt request is automatically generated at the end of 16-bit shifting.

- 4. In the ADDASIO interrupt routine, read the channel information (ADDACON.5) and read/write ADC/DAC data corresponding channel.

- 5. Repeat steps 3 to 4.

- NOTE: CS4216: analog-to-digital/digital-to-analog converter device supplied by Crystal Semiconductor Corporation in U.S.A.

### ADDASIO CONTROL REGISTER (ADDACON)

The control register for ADDASIO interface module, ADDACON, is located at 4CH. It has the control settings for the ADDASIO module.

- Channel 0 Interrupt enable

- Channel 1 Interrupt enable

- Edge selection for shift operation

- IIS format

- Shift operation (transmit/receive) enable

- Channel information.

A reset clears the ADDACON value to '00H'. This means that Tx and Rx are at rising edges and selects the IIS format so that the transition of CFSYNC (Frame sync.) occurs one clock cycle earlier(i.e. together with the last bit of the previous data word). The data shift operation and the interrupt are disabled.

Figure 16-1. ADC/DAC Serial I/O Module Control Register (ADDACON)

Figure 16-2. ADC/DAC Serial I/O Module Block Diagram

Figure 16-3. ADC/DAC Serial I/O Module Waves

# **17** MAC816

### **MAC816 ARCHITECTURE OVERVIEW**

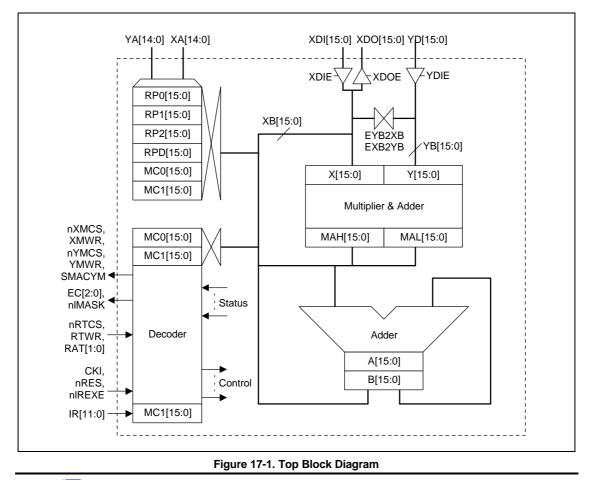

MAC816 is a 16-bit fixed-point DSP coprocessor for low-end DSP applications. It is designed as one of the DSP coprocessor engines for

intended operations on MAC816, including the DSP data type, and the DSP addressing mode. Below represented is the top block diagram of MAC816.

17-1

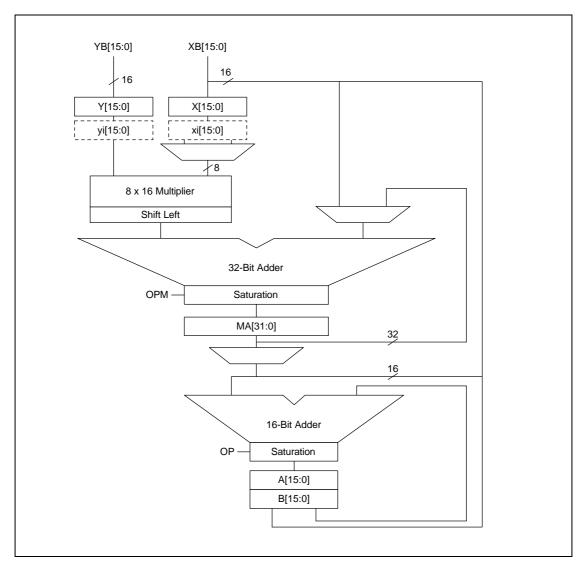

The MAC816 building blocks consist of:

- Multiplier and Accumulator Unit (MAU)

- Arithmetic Unit (AU)

- RAM Pointer Unit (RPU)

- Interface Unit (IU)

Basically, MAU (Multiplier and Accumulator Unit) is built around an 8-bit by 16-bit parallel multiplier and a 32-bit adder for multiply-and-accumulate (MAC) operations. Hence, 16-bit by 16-bit MAC operations are performed in two cycles in MAC816. AU performs 16-bit arithmetic and shift operations for DSP. RPU of MAC816 consists of 3 data memory pointers and 2 control blocks for the pointer modulo calculation. The pointers are used for accessing the data memory for a 16-bit data operand. Since two 16-bit data operands can be fetched simultaneously in a single cycle through XD[15:0] and YD[15:0] for MAC operation, the data memory should be partitioned into two parts: X and Y memory. IU is used for the communication between CalmRISC and MAC816. It decodes coprocessor interface signals from CalmRISC and controls the data paths in MAC816, according to the decoding result.

Most of MAC816 instructions are 1-word instruction, while several instructions which need 16-bit immediate value are 2-word instruction.

#### **PROGRAMMER'S MODEL**

In this chapter, the important features of MAC816 are discussed in detail. How the data memory is organized is discussed and the explanation of registers follows. Last, the host interface with CalmRISC will be explained.

#### DATA MEMORY ACCESSES

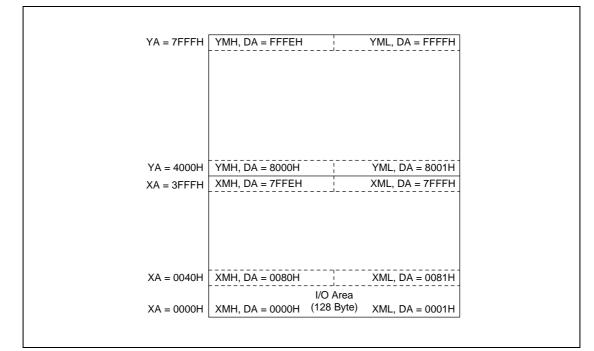

The total data memory address space for MAC816 is 32 kword. The 32 kword data memory space is physically divided into XM (X area memory) and YM (Y area memory). This memory space is actually shared with the host processor (CalmRISC). The host processor accesses the 64K byte data memory in byte width, otherwise MAC816 accesses it in 2-byte width. MAC816 has two types of addressing modes. RPU can generate two 15-bit addresses every instruction cycle which can be post-modified.

Figure 17-2. Data Memory Organization

| Registers |     | Mnemonics | Description                             | Reset Value |

|-----------|-----|-----------|-----------------------------------------|-------------|

| Mreg1     | RPi | RP0       | RAM Pointer register 0                  | Unknown     |

|           |     | RP1       | RAM Pointer register 1                  | Unknown     |

|           |     | RP2       | RAM Pointer register 2                  | Unknown     |

|           |     | RPD       | RAM Pointer for short direct addressing | Unknown     |

| MCi       |     | MC0       | Modulo Control register 0 for RP0/RP1   | Unknown     |

|           |     | MC1       | Modulo Control register 1 for RP2       | Unknown     |

Table 18-1. RPU(RAM Pointer Unit) Registers

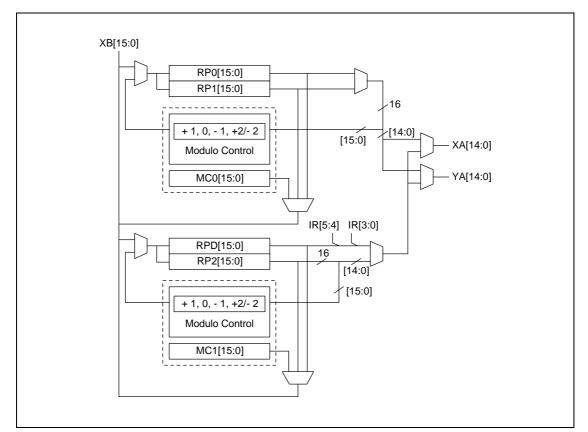

Figure 17-3. RPU(RAM Pointer Unit) Block Diagram

#### Short Direct Memory Addressing Mode